- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367822 > PCI9060SD (Electronic Theatre Controls, Inc.) 12O COMPATIBLE PCI BUS MASTER INTERFACE CHIP FOR ADAPTERS AND EMBEDDED SYSTEMS PDF資料下載

參數(shù)資料

| 型號(hào): | PCI9060SD |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 12O COMPATIBLE PCI BUS MASTER INTERFACE CHIP FOR ADAPTERS AND EMBEDDED SYSTEMS |

| 中文描述: | 12O兼容的PCI總線主控接口芯片的適配器和嵌入式系統(tǒng) |

| 文件頁(yè)數(shù): | 55/192頁(yè) |

| 文件大小: | 1551K |

| 代理商: | PCI9060SD |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)當(dāng)前第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)

SECTION 4

PCI 9080

REGISTERS

PLX Technology, Inc., 1997

Page 46

Version 1.02

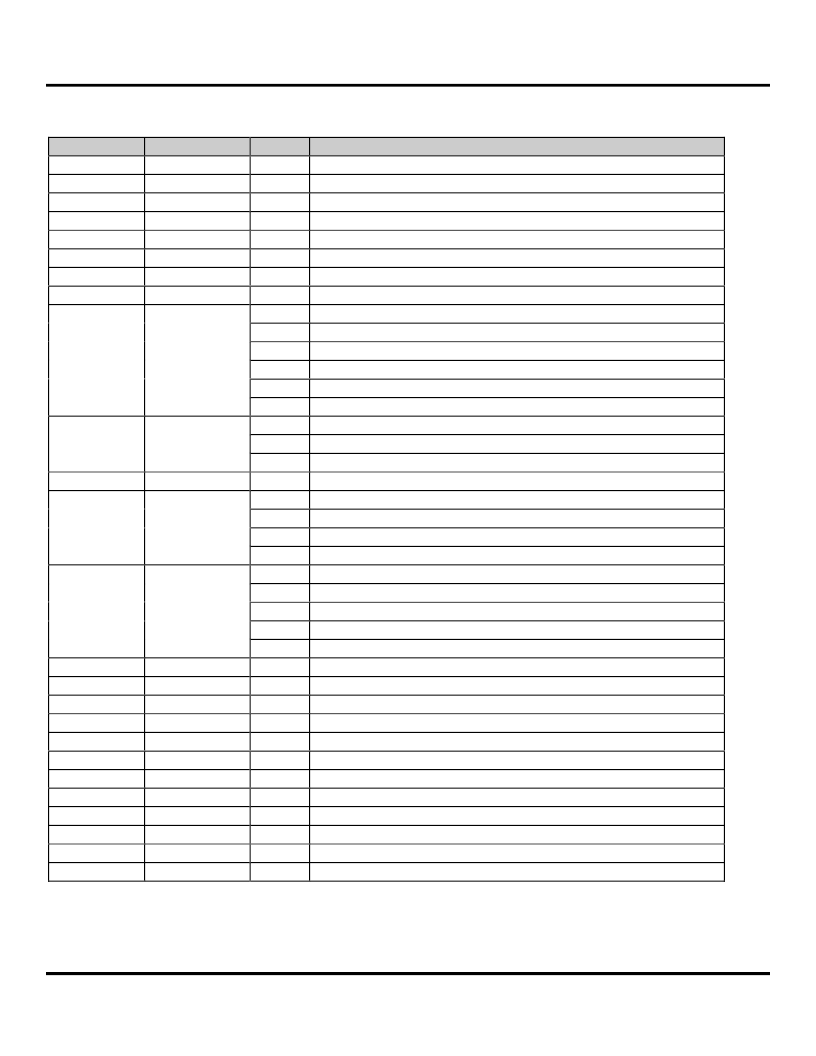

Table 4-3. Register Differences between PCI 9080 and PCI 9060ES

Register

PCI/Local Offset

Bits

Description

PCIIDR

00/00

31:16

Default changed from PCI 906E to PCI 9080

PCISR

06/06

6

User definable bit added

PCICLSR

0C/0C

7:0

Cache line size is now used for Memory Write and Invalidate

PCIBAR0

10/10

8:6

Register Bank size changed from 128 to 256

PCIBAR1

14/14

8:6

Register Bank size changed from 128 to 256

PCIBAR3

1C/1C

31:0

Base address register for Local Address Space 1

PCISVID

2C/2C

15:0

Subsystem Vendor ID Register

PCISID

2E/2E

15:0

Subsystem ID Register

20:19

DMA Channel Priority

23

PCI Request Mode

25

PCI Read/No Write Mode

26

PCI Read with Write Flush Mode

27

Get the Local Bus Latency Timer with BREQ

MARBR

08, AC/88, 12C

28

PCI Read/No Flush Mode

5

Direct Slave Big Endian Mode

6

DMA Channel 1 Big Endian Mode

BIGEND

0C/8C

7

DMA Channel 0 Big Endian Mode

EROMBA

14/94

5

BREQo Timer Resolution control

1:0

Local bus width now programmable in S mode

15

Single Read Access Mode removed

17:16

Local bus width now programmable in S mode

LBRD0

18/98

25

Extra long serial EEPROM load bit

12, 3

Direct Master Read Prefetch Size Control

10, 8:5

Programmable Almost Full Flag increased by one bit

11

Direct Master Prefetch Limit

13

I/O Remap select

DMPBAM

28/A8

15:14

Direct Master Write Delay

LAS1RR

F0/170

31:0

Local Address Space 1 Range Register

LAS1BA

F4/174

31:0

Local Address Space 1 Local Base Address Register (Remap)

LBRD1

F8/178

31:0

Local Address Space 1 Bus Region Descriptor Register

MBOX0

40, 78/C0

31:0

MBOX0 moved to PCI address 78 when Messaging Queue is enabled

MBOX1

44, 7C/C4

31:0

MBOX1 moved to PCI address 7C when Messaging Queue is enabled

MBOX4

50/D0

31:0

MBOX4 added

MBOX5

54/D4

31:0

MBOX5 added

MBOX6

58/D8

31:0

MBOX6 added

MBOX7

5C/DC

31:0

MBOX7 added

P2LDBELL

60/E0

31:8

24 more doorbell bits added to PCI to Local Doorbell Register

L2PDBELL

64/E4

31:8

24 more doorbell bits added to Local to PCI Doorbell Register

INTCSR

68/E8

3

Mailbox Interrupt Enable

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI950PT | PC Card Support |

| PCI9656-AC66BI | Controller Miscellaneous - Datasheet Reference |

| PCIB40 | PC(ISA)BUS I/O CARD |

| PCICLOCKGEN_R001 | AMD Alchemy? Solutions Au1500? PCI Clock Generation? |

| PCK2000 | CK97 (66/100MHz) System Clock Generator(CK97 (66/100MHz) 系統(tǒng)時(shí)鐘發(fā)生器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI9060SD-1AF | 功能描述:數(shù)字總線開關(guān) IC PCI Bus Interface RoHS:否 制造商:Texas Instruments 開關(guān)數(shù)量:24 傳播延遲時(shí)間:0.25 ns 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TSSOP-56 封裝:Reel |

| PCI9080 | 制造商:PLX 制造商全稱:PLX 功能描述:I2O Compatible PCI Bus Master I/O Accelerator Chip |

| PCI9080 REV3 | 制造商:PLX TECH 功能描述: |

| PCI9080-3 | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI I2O Compatible PCI BUS MASTER I/O CHIP RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI9080-3 G | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 32Bit Master Chip RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。