- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296800 > PEF22508E (INFINEON TECHNOLOGIES AG) DATACOM, PCM TRANSCEIVER, PBGA256 PDF資料下載

參數(shù)資料

| 型號: | PEF22508E |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | DATACOM, PCM TRANSCEIVER, PBGA256 |

| 封裝: | 17 X 17 MM, 1 MM PITCH, PLASTIC, LBGA-256 |

| 文件頁數(shù): | 94/193頁 |

| 文件大?。?/td> | 10683K |

| 代理商: | PEF22508E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁當(dāng)前第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁

Data Sheet

183

Rev. 1.0, 2005-06-02

OctalLIU

TM

PEF 22508 E

Operational Description

Features like alarm simulation etc. are activated later. Transmission of alarms (e.g. AIS, remote alarm) and control

of synchronization in connection with consequent actions to remote end and internal system depend on the

activation procedure selected.

Note: Read access to unused register addresses: value should be ignored. Write access to unused register

addresses: should be avoided, or set to “00” hex. All control registers (except XS(16:1), CMDR, DEC) are of

type Read/Write.

Specific E1 Register Settings

The following is a suggestion for a basic configuration to meet most of the E1 requirements. Depending on different

applications and requirement any other configuration can be used.

Attention: After the device configuration a software reset should be executed by setting of bits

CMDR.XRES/RRES.

7.5

Device Configuration in T1/J1 Mode

After reset, the OctalLIU

TM is initialized for E1 doubleframe format. To configure T1/J1 mode, bit MR1.PMOD has

to be set high. After the internal clocking is settled to T1/J1mode (takes up to 20

s), the following register values

are initialized:

T1/J1 Initialization

For a correct start up of the primary access interface a set of parameters specific to the system and hardware

environment must be programmed after RES goes inactive (high). Both the basic and the operational parameters

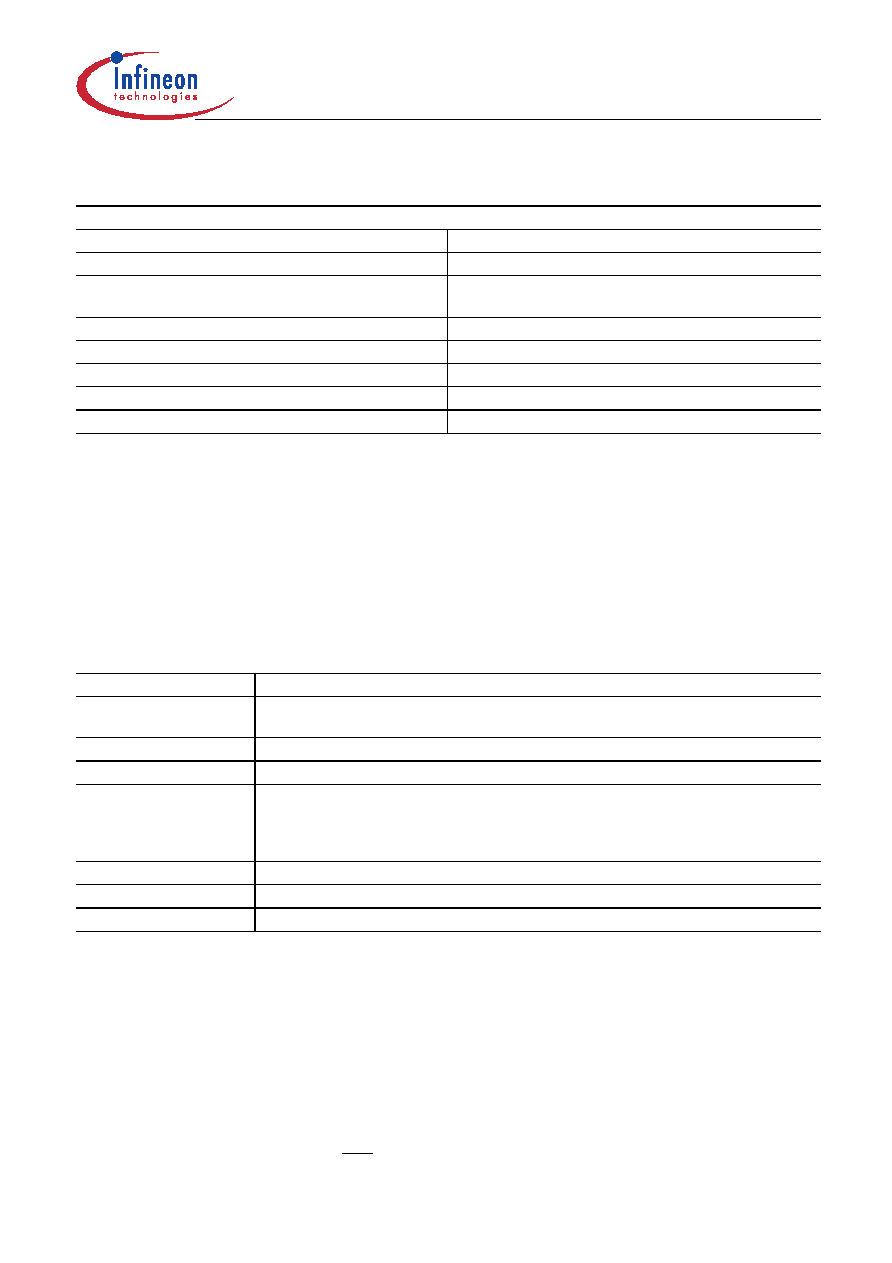

Table 69

Configuration Parameters (E1)

Basic Set Up

Master clocking mode

GCM(6:1) according to external MCLK clock frequency

E1 mode select

MR1.PMOD = 0

Clock system configuration

CMR(3:1), GPC1; if COMP = 0 CMR(6:4) and

GPC(6:2)

Specification of line interface

LIM0, LIM1, XPM(2:0)

Specification of transmit pulse mask

XPM(2:0) or TXP(16:1)

Line interface coding

MR0.XC(1:0), MR0.RC(1:0)

Loss-of-signal detection/recovery conditions

PCD, PCR, LIM1, LIM2

Multi Function Port selection

PC(3:1)

Table 70

Line Interface Configuration (E1)

MR2.DAIS = 1

Disables AIS insertion into the data stream (necessary for proper operation)

MR2.RTM = 1

Sets the receive dual elastic store in a “free running” mode (necessary for proper

operation)

MR5.TT0 = 1

Enables transmit transparent mode (necessary for proper operation)

MR5.XTM = 1

Sets the transmitter in a “free running” mode (necessary for proper operation)

MR0.XC0/

MR0.RC0/

LIM1.DRS

MR3.CMI

The OctalLIU

TM supports requirements for the analog line interface as well as the

digital line interface. For the analog line interface the codes AMI and HDB3 are

supported. For the digital line interface modes (dual- or single-rail) the OctalLIU

TM

supports AMI, HDB3, CMI (with and without HDB3 precoding).

PCD = 0A

H

LOS detection after 176 consecutive “zeros” (fulfills G.775).

PCR = 15

H

LOS recovery after 22 “ones” in the PCD interval. (fulfills G.775).

LIM1.RIL(2:0) = 02

H

LOS threshold of 0.6 V (fulfills G.775).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PEF22554E | DATACOM, FRAMER, PBGA160 |

| PEF22554HT | DATACOM, FRAMER, PQFP144 |

| PES12-42S-N0024 | |

| PESD3V3V4UK,132 | 25 W, UNIDIRECTIONAL, 4 ELEMENT, SILICON, TVS DIODE |

| PF38F3050L0YUQ3A | SPECIALTY MEMORY CIRCUIT, PBGA88 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PEF22508EV1.1-G | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC T/E RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| PEF22508EV11G | 制造商:Rochester Electronics LLC 功能描述: 制造商:Infineon Technologies AG 功能描述: |

| PEF22508EV11GXP | 制造商:Lantiq 功能描述:LINE INTERFACE UNITS |

| PEF22508EV11GXT | 制造商:Lantiq 功能描述:LINE INTERFACE UNITS |

| PEF22509EV1.1 | 制造商:Infineon Technologies AG 功能描述:SP000205605_T/E ASIC_TY_PB |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。