- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369993 > pentium III processor (Intel Corp.) 32 bit Processor Mobile Module(32 位帶移動模塊處理器) PDF資料下載

參數(shù)資料

| 型號: | pentium III processor |

| 廠商: | Intel Corp. |

| 英文描述: | 32 bit Processor Mobile Module(32 位帶移動模塊處理器) |

| 中文描述: | 32位處理器的移動模塊(32位帶移動模塊處理器) |

| 文件頁數(shù): | 36/67頁 |

| 文件大小: | 834K |

| 代理商: | PENTIUM III PROCESSOR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

Pentium

III Processor Mobile Module MMC-2

Featuring Intel

SpeedStep

Technology

30

Datasheet

243356-005

5.0

Electrical Specifications

The following section provides the electrical specifications for the Pentium

III

processor mobile

module featuring Intel SpeedStep technology.

5.1

System Bus Clock Signal Quality Specifications

The HCLK0 and BCLK signal names are used interchangeably.

5.1.1

BCLK DC Specifications

NOTE:

V

and V

only apply when BCLK is stopped. BCLK should be stopped in the low state. See

Table 20

for the BCLK voltage range specifications when BCLK is running.

5.1.2

BCLK AC Specifications

NOTES:

1. All AC timings for GTL+ and CMOS signals are referenced to the BCLK rising edge at 1.25V. All CMOS

signals are referenced at 0.75V.

2. The internal core clock frequency is derived from the PSB clock. The PSB clock to core clock ratio is

determined during initialization and is predetermined by the Intel mobile module. The BCLK period allows a

+0.5 nS tolerance for clock driver variation.

3. This value is measured on the rising edge of adjacent BCLKs at 1.25V. The jitter present must be accounted

for as a component of BCLK skew between devices.

4. The clock driver's closed loop jitter bandwidth must be set low to allow any PLL-based device to track the

jitter created by the clock driver. The -20 dB attenuation point, as measured into a 10-pF to a 2-pF load,

should be less than 500 kHz. This specification may be ensured by design characterization and/or measured

with a spectrum analyzer. See the

CK97 Clock Synthesizer/Driver Specification (OR-1089)

for further details.

5. These values are not 100% tested and are specified by design characterization as a clock driver

requirement.

6. Specifications labeled N/A are not available.

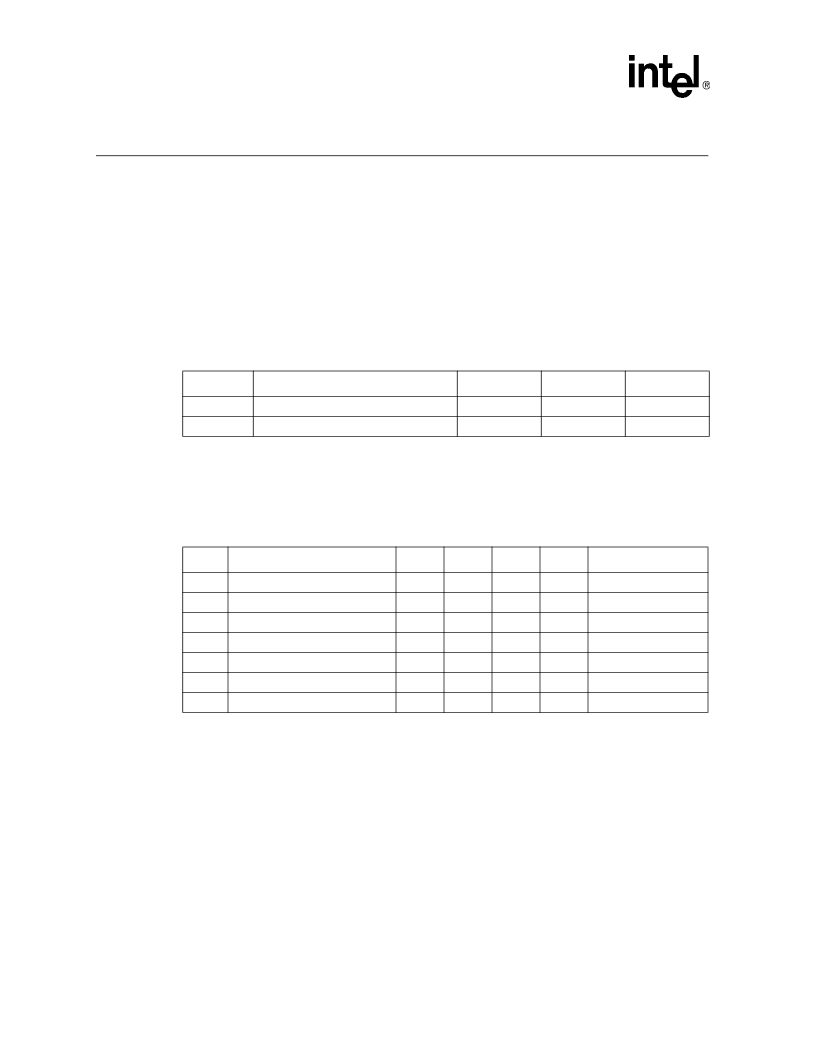

Table 19. BCLK DC Specifications

Symbol

Parameter

Min

Max

Unit

V

IL,BCLK

Input Low Voltage, BCLK

- 0.3

0.5

V

V

IH,BCLK

Input High Voltage, BCLK

2.0

2.625

V

Table 20. BCLK AC Specifications at the Processor Core Pins

T#

Parameter

Min

Nom

Max

Unit

Note

System Bus Frequency

N/A

100.0

N/A

MHz

Notes 5, 6

BCLK Period

N/A

10.0

N/A

nS

Notes 2, 5, 6

BCLK Period Stability

N/A

N/A

±

250

pS

Notes 3, 4, 5, 6

T3:

BCLK High Time

2.85

N/A

N/A

nS

At > 1.7V, Notes 5, 6

T4:

BCLK Low Time

2.55

N/A

N/A

nS

At > 0.7V, Notes 5, 6

T5:

BCLK Rise Time

0.175

N/A

0.875

nS

0.9V ~ 1.6V, Notes 5, 6

T6:

BCLK Fall Time

0.175

N/A

0.875

nS

1.6V ~ 0.9V, Notes 5, 6

相關PDF資料 |

PDF描述 |

|---|---|

| Pentium OverDrive Processor | Pentium OverDrive Processor With MMX Technology For Pentium Processor-Based System(帶MMX技術奔騰超速轉動處理器) |

| pentium pro processor | Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) |

| pentium processor with MMX | 32-bit processor with MMX technology(32位帶MMX技術處理器) |

| pentium processor | 32 Bit Processor With MMX And Mobile Module(32位帶移動模塊和MMX技術CPU) |

| PESD0603-140 | Raychem Overvoltage Devices |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復。