- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1962 > PI7C9X7954AFDE (Pericom)IC PCIE-TO-UART BRIDGE 128LQFP PDF資料下載

參數(shù)資料

| 型號: | PI7C9X7954AFDE |

| 廠商: | Pericom |

| 文件頁數(shù): | 22/70頁 |

| 文件大小: | 0K |

| 描述: | IC PCIE-TO-UART BRIDGE 128LQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 應(yīng)用: | PCIe至UART橋接 |

| 接口: | 高級配置電源接口(ACPI) |

| 電源電壓: | 1.8V, 3.3V |

| 封裝/外殼: | 128-LQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 128-LQFP(14x14) |

| 包裝: | 托盤 |

| 安裝類型: | 表面貼裝 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

PI7C9X7954

PCI Express Quad UART

Datasheet

Page 29 of 70

May 2013 – Revision 1.4

Pericom Semiconductor

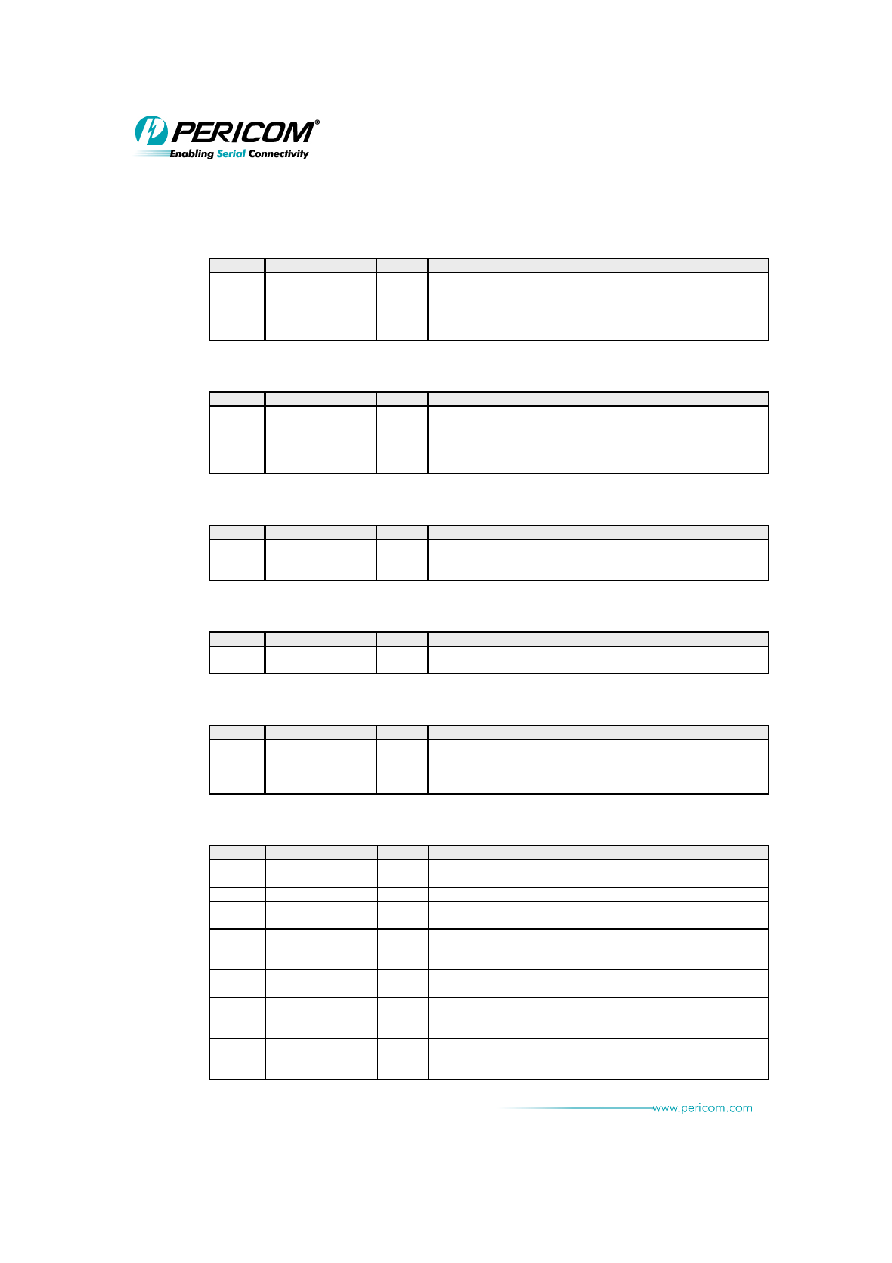

6.2.14. CAPABILITIES POINTER REGISTER – OFFSET 34h

BIT

FUNCTION

TYPE

DESCRIPTION

7:0

Capabilities Pointer

RO

This optional register points to a linked list of new capabilities

implemented by the device. This default value may be changed by

auto-loading from EEPROM.

The default value is 80h.

6.2.15. INTERRUPT LINE REGISTER – OFFSET 3Ch

BIT

FUNCTION

TYPE

DESCRIPTION

7:0

Interrupt Line

RW

Used to communicate interrupt line routing information. POST

software will write the routing information into this register as it

initializes and configures the system.

Reset to 00h.

6.2.16. INTERRUPT PIN REGISTER – OFFSET 3Ch

BIT

FUNCTION

TYPE

DESCRIPTION

15:8

Interrupt Pin

RO

Identifies the legacy interrupt Message(s) the device uses.

Reset to 01h.

6.2.17. POWER MANAGEMENT CAPABILITY ID REGISTER – OFFSET 80h

BIT

FUNCTION

TYPE

DESCRIPTION

7:0

Enhanced

Capabilities ID

RO

Read as 01h to indicate that these are power management enhanced

capability registers.

6.2.18. NEXT ITEM POINTER REGISTER – OFFSET 80h

BIT

FUNCTION

TYPE

DESCRIPTION

15:8

Next Item Pointer

RO

The pointer points to the Power Management capability register

(8Ch).

Reset to 8Ch.

6.2.19. POWER MANAGEMENT CAPABILITIES REGISTER – OFFSET 80h

BIT

FUNCTION

TYPE

DESCRIPTION

18:16

Power Management

Revision

RO

Read as 011b to indicate the I/O bridge is compliant to Revision 1.1

of PCI Power Management Interface Specifications.

19

PME# Clock

RO

Does not apply to PCI Express. Must be hardwired to 0b.

20

Auxiliary Power

RO

Read as 1b to indicate the I/O bridge forwards the PME# message in

D3cold and an auxiliary power source is required.

21

Device Specific

Initialization

RO

Read as 0b to indicate the I/O bridge does not have device specific

initialization requirements. The default value may be changed by

auto-loading from EEPROM.

24:22

AUX Current

RO

Reset as 111b to indicate the I/O bridge need 375 mA in D3 state.

The default value may be changed by auto-loading from EEPROM.

25

D1 Power State

Support

RO

Read as 1b to indicate the I/O bridge supports the D1 power

management state. The default value may be changed by

auto-loading from EEPROM.

26

D2 Power State

Support

RO

Read as 1b to indicate the I/O bridge supports the D2 power

management state. The default value may be changed by

auto-loading from EEPROM.

13-0093

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C9X7958ANBE | IC PCIE-TO-UART BRIDGE 160LFBGA |

| PI90LV017AUEX | IC LVDS DIFF LINE DVR 3V 8-MSOP |

| PI90LV01TEX | IC LVDS DIFF LINE DRVR SOT23-5 |

| PI90LV027AW | IC DUAL LVDS LINE DRIVER 8-SOIC |

| PI90LV028AUEX | IC LVDS LINE RCVR DUAL 8-MSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C9X7958AEVB | 制造商:Pericom Semiconductor Corporation 功能描述:7958A EVAL BOARD 制造商:Pericom Semiconductor Corporation 功能描述:EVAL BOARD PI7C9X7958A 制造商:Pericom Semiconductor Corporation 功能描述:8 Port PCI Express UART I/O Bridge Evaluation Board |

| PI7C9X7958ANBE | 功能描述:外圍驅(qū)動器與原件 - PCI X1 PCIE-UART 8 Channel Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C9X7958ANBE-MOXA | 制造商:Pericom Semiconductor Corporation 功能描述: |

| PI8008 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DIGITAL-THERMOMETER |

| PI80N06S4-05 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:OptiMOS-T2 Power-Transistor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。