- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25640 > S1C63158D0A010P 4-BIT, FLASH, 4 MHz, MICROCONTROLLER, UUC53 PDF資料下載

參數(shù)資料

| 型號: | S1C63158D0A010P |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, FLASH, 4 MHz, MICROCONTROLLER, UUC53 |

| 封裝: | DIE-53 |

| 文件頁數(shù): | 22/159頁 |

| 文件大?。?/td> | 1200K |

| 代理商: | S1C63158D0A010P |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁

110

EPSON

S1C63808 TECHNICAL MANUAL

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (SVD Circuit)

4.13.3 I/O memory of SVD circuit

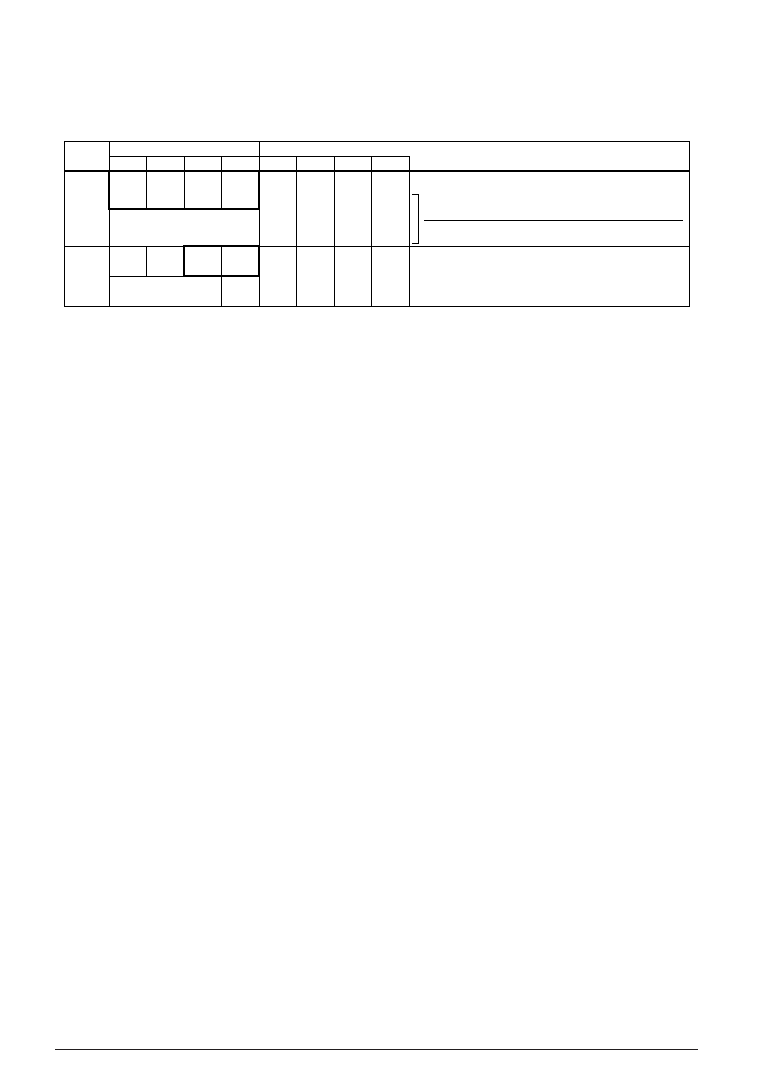

Table 4.13.3.1 shows the I/O addresses and the control bits for the SVD circuit.

Table 4.13.3.1 Control bits of SVD circuit

Address

Comment

D3

D2

Register

D1

D0

Name

Init 1

10

FF05H

00

SVDDT SVDON

RR/W

0 3

SVDDT

SVDON

– 2

0

Low

On

Normal

Off

Unused

SVD evaluation data

SVD circuit On/Off

FF04H

SVDCHG SVDS2 SVDS1 SVDS0

R/W

SVDCHG

SVDS2

SVDS1

SVDS0

0

3.0 V

1.5 V

SVD voltage system selection

SVD criteria voltage setting

1

1.10

1.80

2

1.15

1.90

3

1.20

2.00

4

1.25

2.10

5

1.30

2.40

6

1.40

2.70

7

1.50

2.90

[SVDS2–0]

1.5 V (V)

3.0 V (V)

0

1.05

1.70

*1 Initial value at initial reset

*2 Not set in the circuit

*3 Constantly "0" when being read

SVDCHG: SVD voltage set selection register (FF04HD3)

Selects an SVD criteria voltage combination according to the supply voltage.

When "1" is written: 3.0 V (typ.)

When "0" is written: 1.5 V (typ.)

Reading: Valid

When SVDCHG is set to "1", the 8-level criteria voltage set is configured for a 3.0 V supply voltage and

when it is set to "0", voltages are configured for a 1.5 V supply voltage.

At initial reset, this register is set to "0".

SVDS2–SVDS0: SVD criteria voltage setting registers (FF04HD2–D0)

Criteria voltage for SVD is set as shown in Table 4.13.2.1.

At initial reset, these registers are set to "0".

SVDON: SVD control (on/off) register (FF05HD0)

Turns the SVD circuit on and off.

When "1" is written: SVD circuit ON

When "0" is written: SVD circuit OFF

Reading: Valid

When SVDON is set to "1", a source voltage detection is executed by the SVD circuit. As soon as SVDON

is reset to "0", the result is loaded to the SVDDT latch. To obtain a stable detection result, the SVD circuit

must be on for at least 1 msec.

At initial reset, this register is set to "0".

SVDDT: SVD data (FF05HD1)

This is the result of supply voltage detection.

When "0" is read: Supply voltage (VDD–VSS)

≥ Criteria voltage

When "1" is read: Supply voltage (VDD–VSS) < Criteria voltage

Writing: Invalid

The result of supply voltage detection at time of SVDON is set to "0" can be read from this latch.

At initial reset, SVDDT is set to "0".

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1C7XXXF00E199 | 16-BIT, 90 MHz, RISC MICROCONTROLLER, PQFP |

| S2041 | PHOTO TRANSISTOR DETECTOR |

| S3P44R10 | TRIGGER OUTPUT SOLID STATE RELAY, 4000 V ISOLATION-MAX |

| S3S12P128J0VQK | 16-BIT, MROM, 1.05 MHz, MICROCONTROLLER, PQFP80 |

| MC9S12P128J0CFTR | 16-BIT, FLASH, 1.05 MHz, MICROCONTROLLER, QCC48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1C63408 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63557D04Q000 | 制造商:Seiko Instruments Inc (SII) 功能描述:EPSON MCU 4BIT |

| S1C63567 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63616 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63632 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。