- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T8105A H.100/H.110 Interface and Time-Slot Interchangers PDF資料下載

參數(shù)資料

| 型號: | T8105A |

| 英文描述: | H.100/H.110 Interface and Time-Slot Interchangers |

| 中文描述: | H.100/H.110接口和時隙Interchangers |

| 文件頁數(shù): | 109/112頁 |

| 文件大?。?/td> | 1408K |

| 代理商: | T8105A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁當前第109頁第110頁第111頁第112頁

Lucent Technologies Inc.

105

Advance Data Sheet

November 1999

H.100/H.110 Interfaces and Time-Slot Interchangers

Ambassador T8100A, T8102, and T8105

Appendix B. Minimum Delay and

Constant Delay Connections

(continued)

B.2 Delay Type Definitions

(continued)

B.2.1 Exceptions to Minimum Delay

Up until this point in the discussion, the STRDs have

not been discussed because the

to

and

from

streams

have been irrelevant in the switching process*. Rather

than try to list the exceptions mathematically, a table is

provided. The latencies in these cases may exceed two

frames due to the interaction of the intrinsic pipeline

delays with the double buffering.

Table 83. Table of Special Cases (Exceptions)

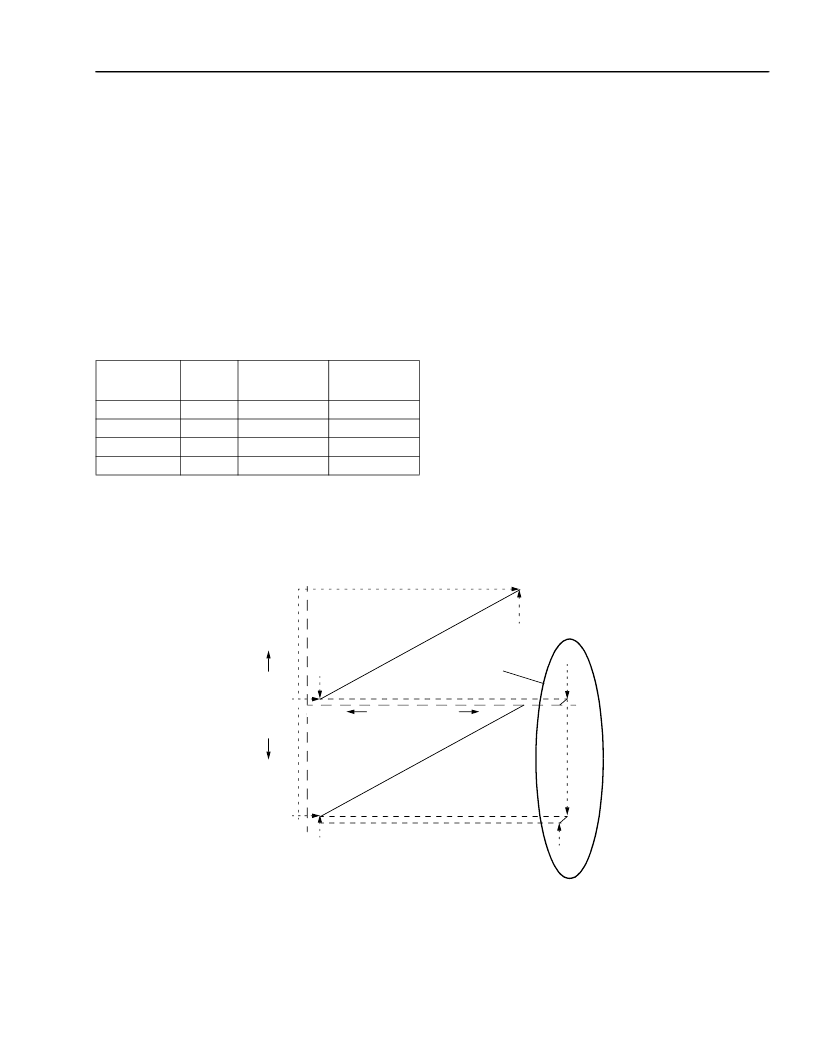

Graphically, the minimum delay latency equations are

illustrated below. The exceptions to the minimum delay

have been included in the diagram, connected to the

main function by dashed lines.

FME Value

TS

Latency for

STR

< 0

257

258

258

257

Latency for

STR

≥

0

257

2

2

257

0

0

1

1

+1

+2

–126

–127

B.2.2 Lower Stream Rates

The discussion has centered on 128 time-slot frames

which correspond to 8.192 Mbits/s data rates. How

does one make similar predictions for lower stream

rates

For 4.096 Mbits/s, multiply the

to

and

from

time-slot

values by two (i.e., time slot 0 at 4.096 Mbits/s corre-

sponds to time slot 0 at 8.192 Mbits/s, and time slot

63 at 4.096 Mbits/s corresponds to time slot 126 at

8.192 Mbits/s). Similarly, multiply values by four to con-

vert 2.048 Mbits/s values. The latency equations can

then be applied directly.

* The one universally disallowed connection on the devices is a TS

of 0 and a STR

of 0. This is a stream and time-slot switching to

itself. Loopback on the local bus (e.g., LDO_0 to LDI_0) is permissi-

ble.

5-6224(F)

Figure 40. Minimum Delay Connections, CON[1:0] = 0X

A

(

RESULTING LATENCY

(TIME SLOTS)

–127

0

127

127

128......256

FME=1

FME=0

0

–126

258

257

2

2

2

SPECIAL LONG LATENCY

CONNECTIONS

(SEE TEXT)

相關PDF資料 |

PDF描述 |

|---|---|

| T8100 | H.100/H.110 Interface and Time-Slot Interchanger |

| T8110 | Version History |

| T8301 | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

| T8302 | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| T8502 | T8502 and T8503 Dual PCM Codecs with Filters |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| T810-600B | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復通態(tài)電流:120 A 額定重復關閉狀態(tài)電壓 VDRM:600 V 關閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:TO-220AB |

| T810-600B | 制造商:STMicroelectronics 功能描述:TRIAC 8A 600V D-PAK |

| T810-600B-TR | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復通態(tài)電流:120 A 額定重復關閉狀態(tài)電壓 VDRM:600 V 關閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:TO-220AB |

| T810-600G | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復通態(tài)電流:120 A 額定重復關閉狀態(tài)電壓 VDRM:600 V 關閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:TO-220AB |

| T810-600G-TR | 功能描述:雙向可控硅 8.0 Amp 600 Volt RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復通態(tài)電流:120 A 額定重復關閉狀態(tài)電壓 VDRM:600 V 關閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:TO-220AB |

發(fā)布緊急采購,3分鐘左右您將得到回復。