- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T8105A H.100/H.110 Interface and Time-Slot Interchangers PDF資料下載

參數(shù)資料

| 型號: | T8105A |

| 英文描述: | H.100/H.110 Interface and Time-Slot Interchangers |

| 中文描述: | H.100/H.110接口和時隙Interchangers |

| 文件頁數(shù): | 72/112頁 |

| 文件大?。?/td> | 1408K |

| 代理商: | T8105A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁當前第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

68

Lucent Technologies Inc.

Advance Data Sheet

November 1999

H.100/H.110 Interfaces and Time-Slot Interchangers

Ambassador T8100A, T8102, and T8105

2 Architecture and Functional Description

(continued)

2.9 Testing and Diagnostics

(continued)

2.9.2 Diagnostics

(continued)

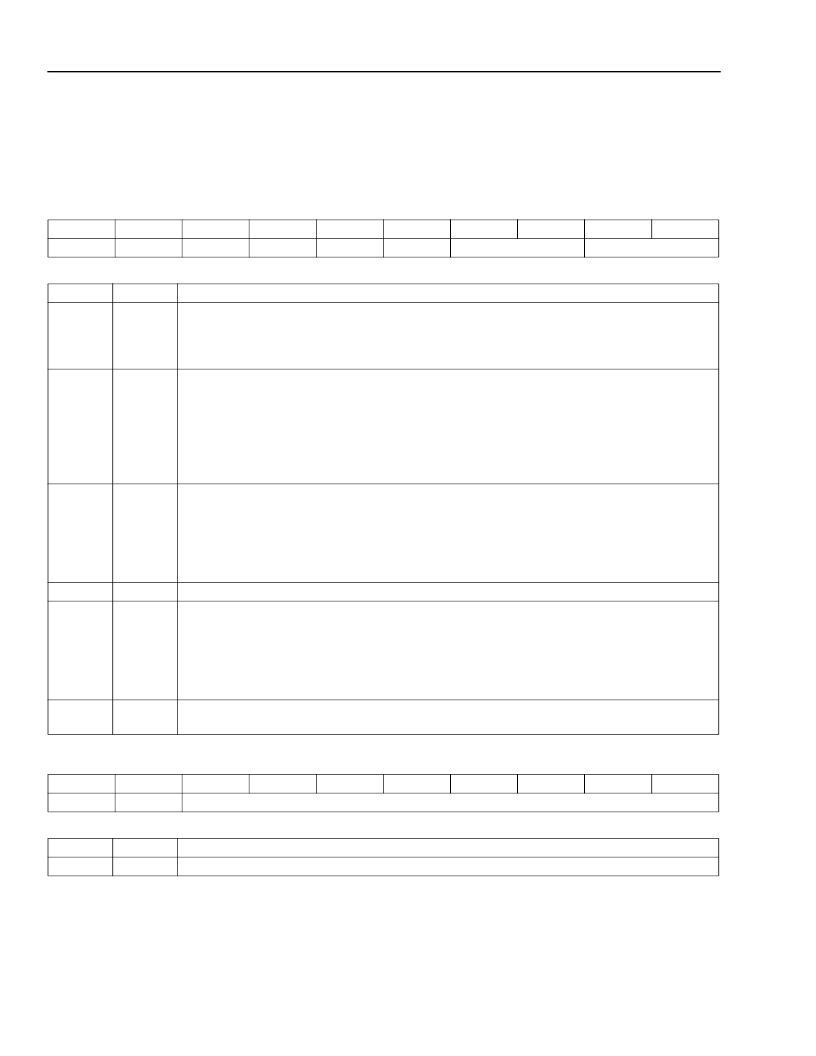

Table 64. DIAG2: Diagnostics Register 2, 0x31

Table 65. DIAG3: Diagnostics Register 3, 0x32

Reg

DIAG2

R/W

—

Bit 7

DFC

Bit 6

DSB

Bit 5

DXF

Bit 4

RES

Bit 3

Bit 2

Bit 1

Bit 0

DSE

DSH

Symbol

DFC

Bit

7

Description

DFC: Diagnostics, Frame Groups Cycle Test

DFC = 0, Normal operation.

DFC = 1, Cycle test mode enabled; forces the frame groups to constantly cycle without

waiting for a frame signal to synchronize the start.

DSB: Diagnostics, State Counter, Break Carry Bits

DSB = 0, Normal operation.

DSB = 1, Breaks the carry bits between the subsections of the state counter so that the

state counter is operating as three counters running in parallel. (This can be

viewed on the frame pins using the DFn = 01 selection described above.) Status

counter bits [0:3] and [4:7] run as modulo-16 counters, and bits [8:10] run as a

modulo-8 counter.

DXF: Diagnostics, External Frame Input

DXF = 0, Normal operation.

DXF = 1, Forces /FR_COMP to act as a direct input signal for devices framing. This effec-

tively bypasses the internally generated frame signal. The user is again cautioned

since the external frame can operate asynchronously to the generated clocks if

care is not taken.

(Reserved.)

DSE: Diagnostics, External Frame Input

DSE = 0, Normal operation.

DSE = 1, Forces the state counter to load the value held in DSH and DSL and continuously

cycle as a modulo-n counter where the n value is determined by (DSH and DSL).

With the DSE pin high, the state counter is no longer synchronized to the frame

signal.

DSH: Diagnostics, State Counter, High Bits of Parallel Load

State counter bits [10:8].

DSB

6

DXF

5

RES

DSE

4

3—2

DSH

1—0

Reg

DSL

R/W

—

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

DSL

Symbol

DSL

Bit

7—0

Description

State counter bits [7:0].

相關PDF資料 |

PDF描述 |

|---|---|

| T8100 | H.100/H.110 Interface and Time-Slot Interchanger |

| T8110 | Version History |

| T8301 | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

| T8302 | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| T8502 | T8502 and T8503 Dual PCM Codecs with Filters |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| T810-600B | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復通態(tài)電流:120 A 額定重復關閉狀態(tài)電壓 VDRM:600 V 關閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:TO-220AB |

| T810-600B | 制造商:STMicroelectronics 功能描述:TRIAC 8A 600V D-PAK |

| T810-600B-TR | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復通態(tài)電流:120 A 額定重復關閉狀態(tài)電壓 VDRM:600 V 關閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:TO-220AB |

| T810-600G | 功能描述:雙向可控硅 8A TRIACS RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復通態(tài)電流:120 A 額定重復關閉狀態(tài)電壓 VDRM:600 V 關閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:TO-220AB |

| T810-600G-TR | 功能描述:雙向可控硅 8.0 Amp 600 Volt RoHS:否 制造商:STMicroelectronics 開啟狀態(tài) RMS 電流 (It RMS):16 A 不重復通態(tài)電流:120 A 額定重復關閉狀態(tài)電壓 VDRM:600 V 關閉狀態(tài)漏泄電流(在 VDRM IDRM 下):5 uA 開啟狀態(tài)電壓: 保持電流(Ih 最大值):45 mA 柵觸發(fā)電壓 (Vgt):1.3 V 柵觸發(fā)電流 (Igt):1.75 mA 最大工作溫度: 安裝風格:Through Hole 封裝 / 箱體:TO-220AB |

發(fā)布緊急采購,3分鐘左右您將得到回復。