- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄365967 > TSB12LV26-EP 672-pin FineLine BGA PDF資料下載

參數(shù)資料

| 型號(hào): | TSB12LV26-EP |

| 英文描述: | 672-pin FineLine BGA |

| 中文描述: | 軍事增強(qiáng)塑料的OHCI -山貓基于PCI的1394主控制器 |

| 文件頁(yè)數(shù): | 51/106頁(yè) |

| 文件大小: | 605K |

| 代理商: | TSB12LV26-EP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)當(dāng)前第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)

3

–

14

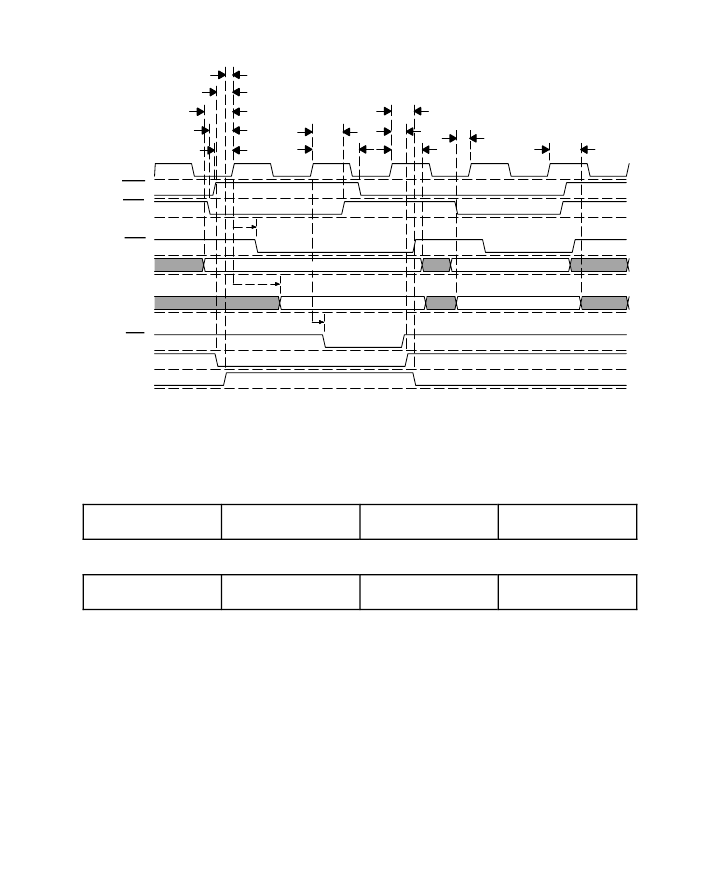

BCLK

MWR

MCS

MCA

MA[0:6]

MD[0:15]

TEA

M8BIT/

SIZ0

MCMODE/

SIZ1

XX

XX

XX

XXXX

XXXX

XXXX

S0

S1

D0

S2

H0

H1

H2

S3

S4

H3

H4

D2

D1

S5

H5

ADDRESS

DATA

ADDRESS

DATA

3.3.5

The term

endianness

refers to the way data is referenced and stored in a processor

’

s memory. For example,

consider a 32-bit processor; any 32-word consists of four bytes which may be stored in memory in one of

two ways. Of the four bytes, either byte 3 will be considered the most significant byte and byte 0 the least

significant byte, or vice versa (see Figures 3

–

15 and 3

–

16). A little endian type memory considers byte 0

the least significant byte, whereas a big endian type memory considers byte 3 to be the least significant byte.

Endian Swapping

Byte #0

(Most Significant Byte)

Byte #1

Byte #2

Byte #3

(Least Significant Byte)

Figure 3

–

15. Big Endian Format

Byte #3

(Most Significant Byte)

Byte #2

Byte #1

Byte #0

(Least Significant Byte)

Figure 3

–

16. Little Endian Format

The TSB12LV32 configuration register space (CFR) and FIFO memory, both of which are 32-bits wide, use

a big endian architecture. The TSB12LV32 uses the same endianness as the internal P1394 link core. This

means that the most significant byte is the left-most byte (byte 0) and the least significant byte is the right

most byte (byte 3).

3.3.5.1

For little-endian processors, there are two modes of byte swapping, address invariant and data invariant.

Address invariance preserves byte ordering between the internal system (GP2Lynx registers and FIFO) and

external system (microcontroller/processor). Data invariance preserves the bit significance of the data, but

changes the byte significance between the internal and external systems. The MDINV pin controls how the

write/read data is swapped at the data bus (i.e., determines how the received bytes from the microcontroller

are mapped into the TSB12LV32 internal registers and memory space). Note that when the COLDFIRE pin

is high, the MDINV pin has no affect and data is always interpreted in as big endian. Refer to Literature

Data and Address Invariance for Little Endian Processors

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB12LV22PZP | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB12LV26PZ | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB14AA1 | FPGA (Field-Programmable Gate Array) |

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

| TSB14AA1T | FPGA (Field-Programmable Gate Array) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB12LV26IPZT | 功能描述:1394 接口集成電路 OHCI-Lynx PCI-Based Host Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV26IPZTEP | 制造商:Texas Instruments 功能描述:1394 I-TEMP OHCI-LYNX PCI-BASED IEEE 1394 HOST CONTROLLER - Rail/Tube |

| TSB12LV26PZ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| TSB12LV26PZT | 功能描述:1394 接口集成電路 OHCI-Lynx PCI-Based Host Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV26PZTG4 | 功能描述:1394 接口集成電路 OHCI-Lynx PCI-Based IEEE1394 Host Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。