- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F128 (Intel Corp.) 3 Volt Intel StrataFlash Memory PDF資料下載

參數(shù)資料

| 型號: | 28F128 |

| 廠商: | Intel Corp. |

| 英文描述: | 3 Volt Intel StrataFlash Memory |

| 中文描述: | 3伏特英特爾StrataFlash存儲器 |

| 文件頁數(shù): | 36/58頁 |

| 文件大小: | 380K |

| 代理商: | 28F128 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

28F128J3A, 28F640J3A, 28F320J3A

30

Preliminary

0606_07A

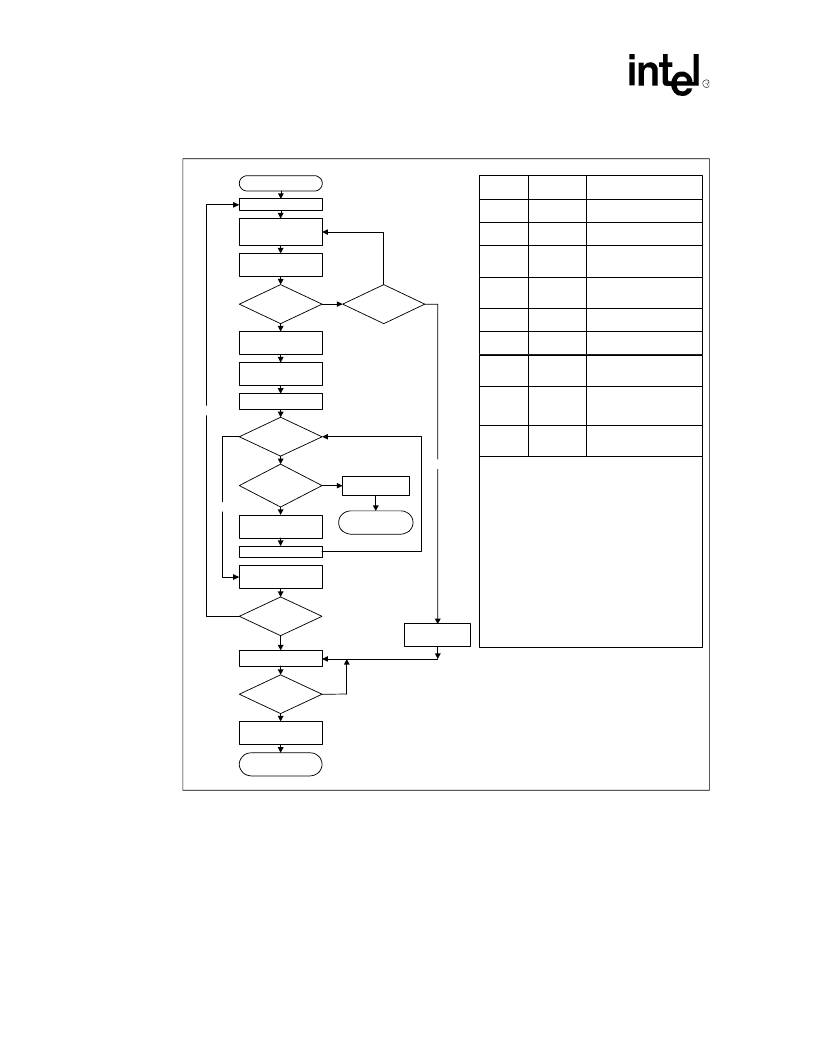

Figure 7. Write to Buffer Flowchart

Start

Write Word or Byte

Count, Block Address

Write Buffer Data,

Start Address

X = 0

X = X + 1

Write Next Buffer Data,

Device Address

Abort Write to

Buffer Command

Check

X = N

Another Write to

Buffer

Read Status Register

SR.7 =

Programming

Complete

Read Extended

Status Register

XSR.7 =

1

No

Yes

No

No

1

Write to Buffer

Aborted

Yes

No

Yes

Full Status

Check if Desired

Program Buffer to Flash

Confirm D0H

Issue Write to Buffer

Command E8H, Block

Address

Write to Another

Block Address

Write to

Buffer Time-Out

0

Set Time-Out

Issue Read

Status Command

Yes

Bus

Operation

Command

Comments

Write

Write to Buffer

Data = E8H

Block Address

Read

XSR. 7 = Valid

Addr = Block Address

Standby

Check XSR. 7

1 = Write Buffer Available

0 = Write Buffer Not Available

Write

(Note 1, 2)

Data = N = Word/Byte Count

N = 0 Corresponds to Count = 1

Addr = Block Address

Write

(Note 3, 4)

Data = Write Buffer Data

Addr = Device Start Address

Write

(Note 5, 6)

Data = Write Buffer Data

Addr = Device Address

Write

Program Buffer

to Flash

Confirm

Data = D0H

Addr = Block Address

Read

(Note 7)

Status Register Data with the

Device Enabled, OE# Low

Updates SR

Addr = Block Address

Standby

Check SR.7

1 = WSM Ready

0 = WSM Busy

1. Byte or word count values on DQ

- DQ

are loaded into the

count register. Count ranges on this device for byte mode are N

= 00H to 1FH and for word mode are N = 0000H to 000FH.

2. The device now outputs the status register when read (XSR is

no longer available).

3. Write Buffer contents will be programmed at the device start

address or destination flash address.

4. Align the start address on a Write Buffer boundary for

maximum programming performance (i.e., A

4

- A

0

of the start

address = 0).

5. The device aborts the Write to Buffer command if the current

address is outside of the original block address.

6. The status register indicates an "improper command

sequence" if the Write to Buffer command is aborted. Follow this

with a Clear Status Register command.

7. Toggling OE# (low to high to low) updates the status register.

This can be done in place of issuing the Read Status Register

command.

Full status check can be done after all erase and write sequences

complete. Write FFH after the last operation to reset the device to

read array mode.

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F1602C3 | 3 Volt Advanced+ Stacked Chip Scale Package Memory(3V閃速存儲器和靜態(tài)存儲器) |

| 28F3204C3 | 3 V Advanced+ Stacked Chip Scale Package Memory(3V高級堆芯片封裝存儲器) |

| 28F1604C3 | 3 Volt Advanced+ Stacked Chip Scale Package Memory(3V閃速存儲器和靜態(tài)存儲器) |

| 28F160C18 | 1.8V Advanced+ Boot Block Flash Memory(1.8V高級引導(dǎo)塊閃速存儲器) |

| 28F160C2 | 2.4V Advanced+ Boot Block Flash Memory(2.4V高級引導(dǎo)塊閃速存儲器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F128J3A | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3 Volt Intel StrataFlash Memory |

| 28F128J3A150 | 制造商: 功能描述: 制造商:INTELC 功能描述: 制造商:undefined 功能描述: |

| 28F128J3A-150 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F128J3D75 | 制造商: 功能描述: 制造商:Intel 功能描述: |

| 28F128J3FS-12ET | 制造商: 功能描述: 制造商:undefined 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。