- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377484 > IDT77V1254L25L25PGI (Integrated Device Technology, Inc.) Quad Port PHY (Physical Layer) for 25.6 and 51.2 ATM Networks PDF資料下載

參數(shù)資料

| 型號: | IDT77V1254L25L25PGI |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | Quad Port PHY (Physical Layer) for 25.6 and 51.2 ATM Networks |

| 中文描述: | 四端口PHY(實體層)為25.6和51.2 ATM網(wǎng)絡 |

| 文件頁數(shù): | 35/47頁 |

| 文件大小: | 840K |

| 代理商: | IDT77V1254L25L25PGI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

35 of 47

September 21, 2001

IDT77V1254L25

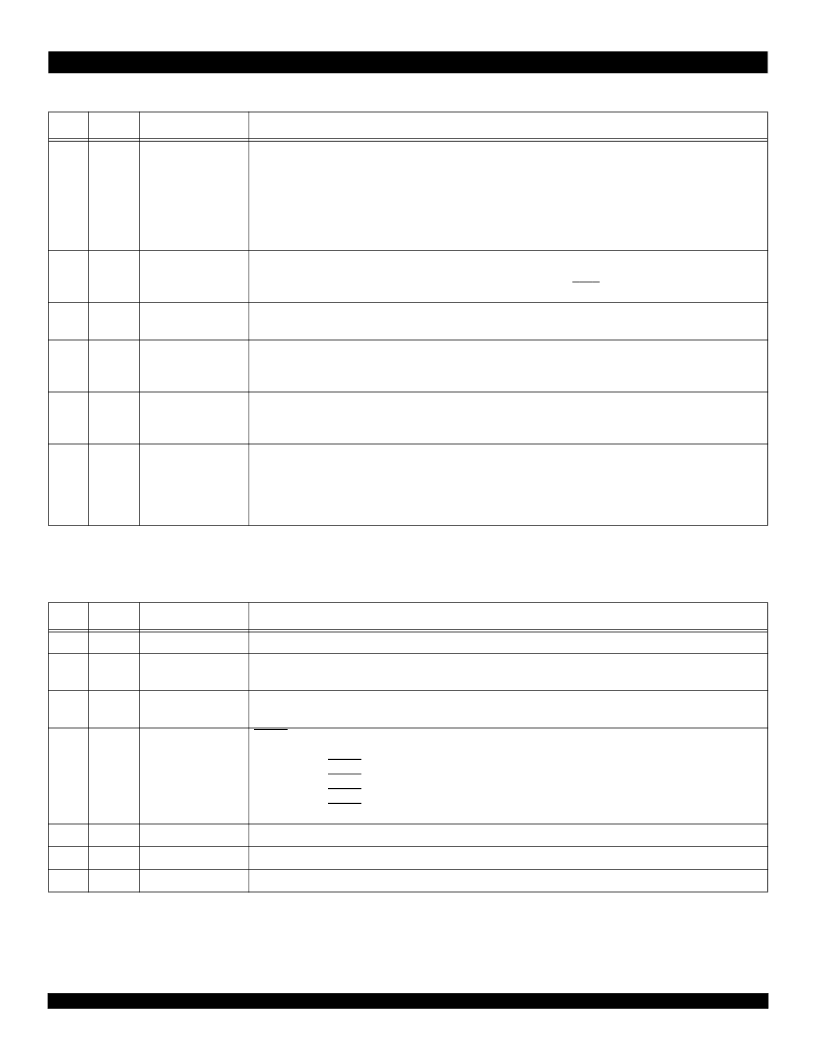

LED Driver and HEC Status/Control Registers

6

R/W

0 = UTOPIA

RXCLAV Operation Select -

(for Utopia 1 mode) The UTOPIA standard dictates that during cell mode operation, if the

receive FIFO no longer has a complete cell available for transfer from PHY, RXCLAV is deasserted following transfer of

the last byte out of the PHY to the upstream system. With this bit set, early deassertion of this signal will occur coinci-

dent with the end of Payload byte 44 (as in octet mode for TXCLAV). This provides early indication to the upstream

system of this impending condition.

0 = "Standard UTOPIA RXCLAV’

1 = "Cell mode = Byte mode"

5

R/W

1 = tri-state

Single/Multi-PHY configuration select -

(applicable and writable only in Utopia 1 mode)

0 = single: Never tri-state RXDATA, RXPARITY and RXSOC

1 = Multi-PHY mode: Tri-state RXDATA, RXPARITY and RXSOC when RXEN = 1

4

R/W

0 = normal

RFLUSH = Clear Receive FIFO -

This signal is used to tell the TC to flush (clear) all data in the receive FIFO. The TC

signals this completion by clearing this bit.

3

R/W

0 = normal

Insert Transmit Payload Error -

Tells TC to insert cell payload errors in transmitted cells. This can be used to test

error detection and recovery systems at destination station, or, under loopback control, at the local receiving station.

This payload error is accomplished by flipping bit 0 of the last cell payload byte.

2

R/W

0 = normal

Insert Transmit HEC Error -

Tells TC to insert HEC error in Byte 5 of cell. This can be used to test error detection and

recovery systems in downstream switches, or, under loopback control, the local receiving station. The HEC error is

accomplished by flipping bit 0 of the HEC byte.

1,0

R/W

00 = normal

Loopback Control

bit # 1 0

0 0 Normal mode (receive from network)

1 0 PHY Loopback

1 1 Line Loopback

Addresses: 0x03, 0x13, 0x23, 0x33

Bit

Type

Initial State

Function

7

0

Reserved

6

R/W

0 = enable checking

Disable Receive HEC Checking (HEC Enable) -

When not set, the HEC is calculated on first 4 bytes of received cell,

and compared against the 5th byte. When set (= 1), the HEC byte is not checked.

5

R/W

0 = enable calculate &

replace

Disable Transmit HEC Calculate & Replace -

When set, the 5th header byte of cells queued for transmit is not

replaced with the HEC calculated across the first four bytes of that cell.

4, 3

R/W

00 = 1 cycle

RXREF Pulse Width Select

bit # 4 3

0 0 RXREF active for 1 OSC cycle

0 1 RXREF active for 2 OSC cycles

1 0 RXREF active for 4 OSC cycles

1 1 RXREF active for 8 OSC cycles

2

R

1 = empty

FIFO Status

1 = TxFIFO empty 0 = TxFIFO not empty

1

R

1

TXLED Status

0 = Cell Transmitted 1 = Cell Not Transmitted

0

R

1

RXLED Status

0 = Cell Received 1 = Cell Not Received

Addresses: 0x02, 0x12, 0x22, 0x32

Bit

Type

Initial State

Function

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT77V1254L25 | Quad Port PHY (Physical Layer) for 25.6 and 51.2 ATM Networks |

| IDT77V1254L25L25PG | Quad Port PHY (Physical Layer) for 25.6 and 51.2 ATM Networks |

| IDT79RC64V475250DZ | RISControllerTM Embedded 64-bit Microprocessor, based on RISCore4000 |

| IDT79RC64V475250DZI | RISControllerTM Embedded 64-bit Microprocessor, based on RISCore4000 |

| IDT79RC64V474180DZI | RISControllerTM Embedded 64-bit Microprocessor, based on RISCore4000 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT77V252L155PG | 制造商:Integrated Device Technology Inc 功能描述:ATM/SONET SEGMENTATION AND REASSEMBLY CIRCUIT, 208 Pin, Plastic, QFP |

| IDT77V400S156BC | 功能描述:IC SW MEMORY 8X8 1.2BGPS 256-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:SwitchStar™ 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT77V400S156BCG | 功能描述:IC SW MEMORY 8X8 1.2BGPS 256-BGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:SwitchStar™ 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT77V400S156DS | 功能描述:IC SW MEMORY 8X8 1.2BGPS 208PQFP RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:SwitchStar™ 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT77V500S25BC | 功能描述:IC SW MEMORY 8X8 1.2BGPS 144-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:SwitchStar™ 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調(diào)幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

發(fā)布緊急采購,3分鐘左右您將得到回復。