- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377488 > IDT88P8344BHGI (INTEGRATED DEVICE TECHNOLOGY INC) SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 PDF資料下載

參數(shù)資料

| 型號(hào): | IDT88P8344BHGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPI EXCHANGE 4 x SPI-3 TO SPI-4 Issue 1.0 |

| 中文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA820 |

| 封裝: | GREEN, PLASTIC, BGA-820 |

| 文件頁(yè)數(shù): | 63/98頁(yè) |

| 文件大小: | 601K |

| 代理商: | IDT88P8344BHGI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)當(dāng)前第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)

63

IDT88P8344 SPI EXCHANGE 4 x SPI-3 TO SPI-4

INDUSTRIAL TEMPERATURE RANGE

APRIL 10, 2006

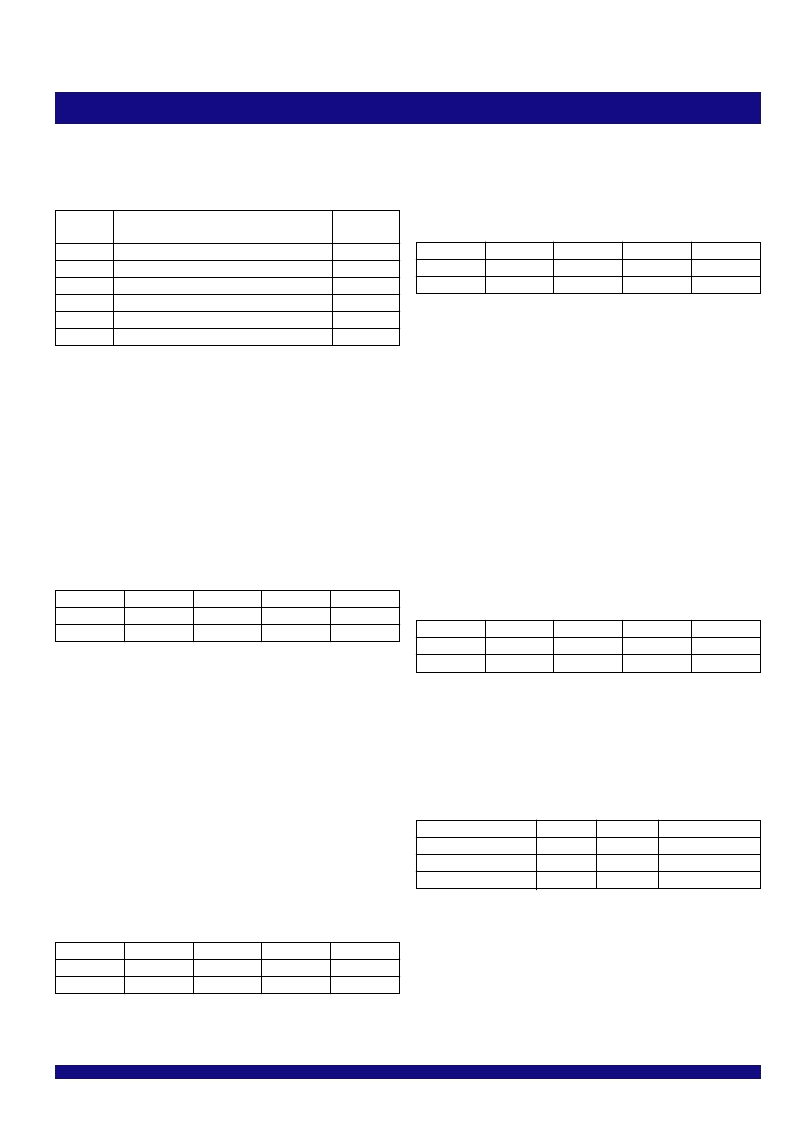

Non critical LID associated capture table

(Block_base 0x0C00 + Register_offset 0x10-0x15)

TABLE 66 - NON CRITICAL LID ASSOCIATED

CAPTURE TABLE (REGISTER_OFFSET 0x10-0x15)

Register

EVENT_TYPE

The Non critical LID associated capture table is at Block_Base 0x0C00 +

Register_Offset 0x10-0x15. The Non critical LID associated capture table is

used to determne the EVENT_TYPE of SPI-3 and SPI-4 per-LID or per-LP

interrupts. The EVENT_TYPE coding is used to indicate which event or events

are pertinent to the interrupt in the Table 64 - LID associated interrupt indication

register(0x0E). The Non critical LID associated capture table is used to

determne the EVENT, and multiple bits can be active at the same time. The Non

critical LID associated capture table is read-only.

SPI-3 to SPI-4 critical LID interrupt indication

registers (Block_base 0x0C00 + Register_offset

0x16-0x17)

TABLE 67 - SPI-3 TO SPI-4 CRITICAL LID INTER-

RUPT INDICATION REGISTERS

(REGISTER_OFFSET 0x16-0x17)

Register

Field

Bits

0x16

LID[31:0]

31:0

0x17

LID[63:32]

31:0

The SPI-3 to SPI-4 critical LID interrupt indication registers are at Block_Base

0x0C00 + Register_offset 0x16-0x17.

Critical events are captured per LID in the SPI-3 to SPI-4 critical LID interrupt

indication registers. An interrupt is generated when enabled by the enable flag

in the SPI-3 to SPI-4 critical LID interrupt enableregisters. A SPI-3 to SPI-4 critical

LID interrupt indication register has read and write access. An interrupt indication

is cleared by writing a logical one to the appropriate bit of a SPI-3 to SPI-4 critical

LID interrupt indication register. Only one kind of critical event is defined-buffer

overflow. Each bit of the LID field set to logical one indicates the presence of a

buffer overflow event. A summary indication of as to which of the two sources,

SPI-3 to SPI-4 or SPI-4 to SPI-3, is responsible for the critical interrupt is indicated

in the Table 71 Critical events source indication register (0x1E).

SPI-3 to SPI-4 critical LID interrupt enable regis-

ters (Block_base 0x0C00 + Register_offset 0x18-

0x19)

TABLE 68 - SPI-3 TO SPI-4 CRITICAL LID INTERRUPT

ENABLE REGISTERS (REGISTER_OFFSET 0x18-

0x19)

Register

Field

Bits

0x18

LID[31:0]

31:0

0x19

LID[63:32]

31:0

The SPI-3 to SPI-4 critical LID interrupt enable registers have read and write

access. A SPI-3 to SPI-4 critical LID interrupt enable register bits enable the

corresponding bits in a SPI-3 to SPI-4 critical LID interrupt indication register.

Associated

field

LP (8 bits)

LID (6 bits)

LID (6 bits)

LID (6 bits)

LID (6 bits)

LID (6 bits)

0x00

0x01

0x02

0x03

0x04

0x05

Inactive ingress SPI-3 logical port event

SPI-3 ingress data parity error

SPI-4 illegal SOP sequence event

SPI-4 illegal EOP sequence event

SPI-3 illegal SOP sequence event

SPI-3 illegal EOP sequence event

Length

32

32

Initial Value

0x00

0x00

Length

32

32

Initial Value

0x00

0x00

SPI-4 to SPI-3 critical LID interrupt indication

registers (Block_base 0x0C00 + Register_offset

0x1A-0x1B)

TABLE 69 - SPI-4 TO SPI-3 CRITICAL LID INTERRUPT

INDICATION REGISTERS (REGISTER_OFFSET

0x1A-0x1B)

Register

Field

Bits

0x1A

LID[31:0]

31:0

0x1B

LID[63:32]

31:0

Length

32

32

Initial Value

0x00

0x00

The SPI-4 to SPI-3 critical LID interrupt indication registers are at Block_Base

0x0C00 + Register_offset 0x1A-0x1B.

Critical events are captured per LID in a SPI-4 to SPI-3 critical LID interrupt

indication register. An interrupt is generated when enabled by the enable flag

in the SPI-4 to SPI-3 critical LID interrupt enableregister. The SPI-4 to SPI-3

critical LID interrupt indication registers have read and write access. An interrupt

indication is cleared by writing a logical one to the appropriate bit of a SPI-4 to

SPI-3 critical LID interrupt indication register. Only one kind of critical event is

defined-buffer overflow. Each bit of a LID field set to logical one indicates the

presence of a buffer overflow event. A summary indication of as to which of the

two sources, SPI-3 to SPI-4 or SPI-4 to SPI-3, is responsible for the critical

interrupt is indicated in the Table 71 Critical events source indication register

(0x1E).

SPI-4 to SPI-3 critical LID interrupt enable regis-

ters (Block_base 0x0C00 + Register_offset 0x1C-

0x1D)

TABLE 70 - SPI-4 TO SPI-3 CRITICAL LID INTER-

RUPT ENABLE REGISTERS (REGISTER_OFFSET

0x1C-0x1D)

Register

Field

Bits

0x1C

LID[31:0]

31:0

0x1D

LID[63:32]

31:0

Length

32

32

Initial Value

0x00

0x00

The SPI-4 to SPI-3 critical LID interrupt enable registers have read and write

access. The SPI-4 to SPI-3 critical LID interrupt enable register bits enable the

corresponding bits in the SPI-4 to SPI-3 critical LID interrupt indication registers.

Critical events source indication register

(Block_base 0x0C00 + Register_offset 0x1E)

TABLE 71 - CRITICAL EVENTS SOURCE INDICA-

TION REGISTER (REGISTER_OFFSET 0x1E)

Field

Bits

SPI34_OVR

0

SPI43_OVR

1

Reserved

31:2

Length

1

1

30

Initial Value

0b0

0b0

0x0

The bits in the Critical events source indication register are read only. Bit

SPI34_OVR reflects the logical OR result of all bits in the SPI-3 to SPI-4 critical

LID associated interrupt indication registers. Bit SPI43_OVR reflects the logical

OR result of all bits in the SPI-4 to SPI-3 critical LID interrupt indication registers.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDTAMB0480 | ADVANCED MEMORY BUFFER FOR FULLY BUFFERED DIMM MODULES |

| IDTCSP2510DPGI | 3.3V PHASE-LOCK LOOP CLOCK DRIVER ZERO DELAY BUFFER |

| IDTCSP2510DPG | SENSOR OPTICAL SLOTTED 1.0MM |

| IDTCSP2510D | 3.3V PHASE-LOCK LOOP CLOCK DRIVER ZERO DELAY BUFFER |

| IDTCSPT857CNL | 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT88P8344BHI | 功能描述:IC SPI3-SPI4 EXCHANGE 820-PBGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:* 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBC8 | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBCG | 功能描述:IC PCI SW 10LANE 4PORT 324BGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:PRECISE™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT89H10T4BG2ZBBCG8 | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。