- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45218 > MC68HC05C0B (MOTOROLA INC) 8-BIT, 4 MHz, MICROCONTROLLER, PDIP42 PDF資料下載

參數(shù)資料

| 型號: | MC68HC05C0B |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 4 MHz, MICROCONTROLLER, PDIP42 |

| 封裝: | SDIP-42 |

| 文件頁數(shù): | 55/96頁 |

| 文件大?。?/td> | 357K |

| 代理商: | MC68HC05C0B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

MOTOROLA

Section 10: Multi-Function Timer

Page 50

MC68HC05C0 Specification Rev. 1.2

10.3

TIMER COUNTER REGISTER (TCR)

The Timer Counter Register is a read-only register which contains the current value of the

8-bit ripple up-counter at the beginning of the timer chain. This counter is clocked at E

divided by 4 and can be used for various functions including a software input capture.

Extended time periods can be attained using the TOF function to increment a temporary

RAM storage location thereby simulating a 16-bit (or more) counter.

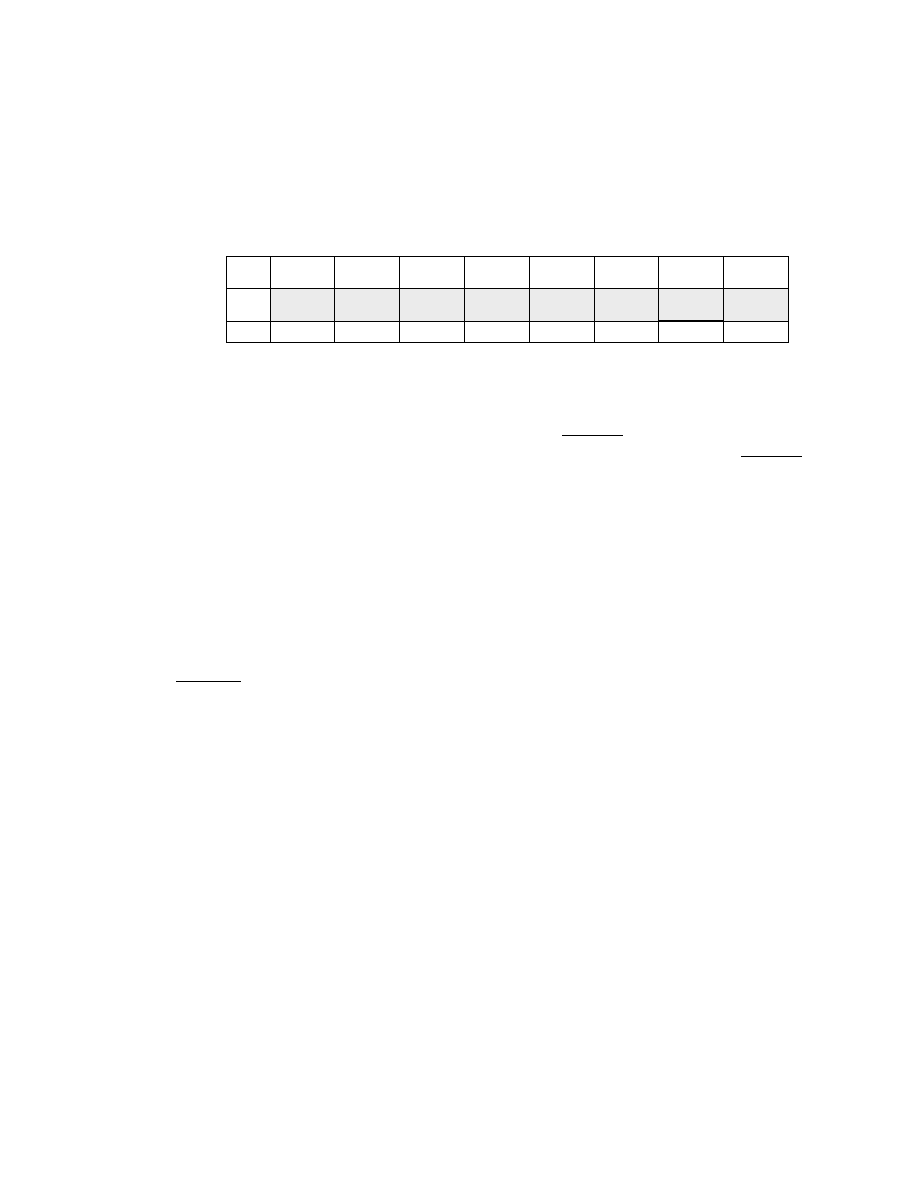

Figure 10-3: Timer Counter Register

The power-on cycle clears the entire counter chain and begins clocking the counter. After

4064 E-cycles, the power-on reset circuit is released which again clears the counter chain

and allows the device to come out of reset. At this point, if RESET is not asserted, the timer

will start counting up from zero and normal device operation will begin. When RESET is

asserted anytime during operation (other than POR), the counter chain will be cleared.

10.4

COMPUTER OPERATING PROPERLY (COP) WATCHDOG RESET

The COP watchdog timer function is implemented on this device by using the output of the

RTI circuit and further dividing it by eight.

The COP is enabled out of reset. The COP can be disabled by writing a logic 0 to the

COPEN bit in the Configuration Register.

If the COP circuit times out, an internal reset is generated and the normal reset vector is

fetched. RESET is also driven low to reset external peripherals. Preventing a COP time-out

is done by writing a logic 0 to bit 0 of address $FFFF at the minimum reset rate. When the

COP is cleared, only the final divide by eight stage (output of the RTI) is cleared.

The minimum COP reset rates are listed in Table 10-2 below. Because it is not readily

possible to determine the state of the divider chain ahead of the COP circuit, the COP

should be reset within a period equivalent to seven real-time interrupts, rather than the

eight that one might expect.

76543210

RD

WR

0

RST

$09

0

TCR

0

DA7

DA6

DA5

DA4

DA3

DA2

DA1

DA0

相關PDF資料 |

PDF描述 |

|---|---|

| MC68HC05C0P | 8-BIT, 4 MHz, MICROCONTROLLER, PDIP40 |

| MC68HC05C0FN | 8-BIT, 4 MHz, MICROCONTROLLER, PQCC44 |

| MC68HC05C12AFN | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PQCC44 |

| MC68HSC05C12AB | 8-BIT, MROM, 4.1 MHz, MICROCONTROLLER, PDIP42 |

| MC68HSC05C12ACP | 8-BIT, MROM, 4.1 MHz, MICROCONTROLLER, PDIP40 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC05C0CP | 制造商:Motorola Inc 功能描述: |

| MC68HC05C12 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNITS |

| MC68HC05C12B | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNITS |

| MC68HC05C12CP | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNITS |

| MC68HC05C12P | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCMOS MICROCONTROLLER UNITS |

發(fā)布緊急采購,3分鐘左右您將得到回復。