- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT90500AL (Mitel Networks Corporation) Multi-Channel ATM AAL1 SAR PDF資料下載

參數(shù)資料

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁

MT90500

12

1.2

Reference Documents

MT90500 Programmer’s Manual.

MSAN-171 - TDM Clock Recovery from CBR-over-ATM Links Using the MT90500.

ITU-T Rec. I.363.1, “B-ISDN ATM Adaptation Layer Specification: Type 1 AAL,” 08/1996.

ANSI T1.630, “Broadband ISDN - ATM Adaptation Layer for Constant Bit Rate Services Functionality and

Specification,” 1993.

AF-PHY-0017, “UTOPIA, An ATM-PHY Interface Specification: Level 1, Version 2.01,” March 21, 1994.

AF-VTOA-0078.000, “Circuit Emulation Service Interoperability Specification, Version 2.0,” Jan. 1997.

AF-VTOA-0083.000, “Voice and Telephony Over ATM to the Desktop Specification, Version 2.0,” May 1997.

M. Noorchasm et al., “Buffer Design for Constant Bit Rate Services in Presence of Cell Delay Variation,” ATM

Forum Contribution 95-1454.

Paul E. Fleischer and Chi-Leung Lau, “Synchronous Residual Time Stamp for Timing Recovery in a Broadband

Network,” United States Patent 5,260,978, Nov. 1993.

IEEE Std. 1149.1a-1993, “IEEE Standard Test Access Port and Boundary Scan Architecture.”

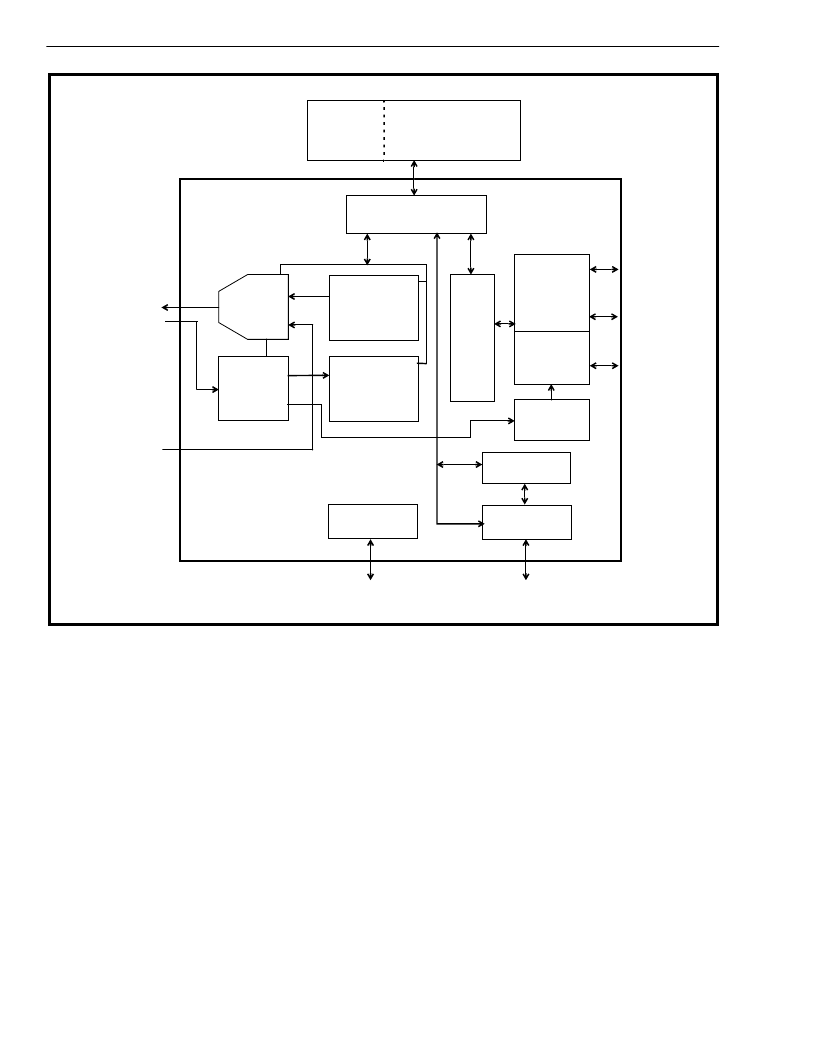

Figure 1 - MT90500 Block Diagram

TDM Bus

Interface

Logic

TX

AAL1

SAR

RX

AAL1

SAR

TDM Bus

16 lines

2048 x 64kbps

(max.)

TX UTOPIA

MUX

RX

UTOPIA

BLOCK

VC Look-up

Tables

TX / RX Control

Structures and

Circular Buffers

Main

UTOPIA

Interface

Secondary

UTOPIA

Interface

Boundary-

Scan Logic

From

External

SAR

To/From

External

PHY

JTAG Interface

16-bit Microprocessor Inter-

face

External Memory

Controller

TDM Clock

Logic

Clock

Signals

External

Synchronous

SRAM

TDM Module

Internal

TDM

Frame

Buffer

Microprocessor

Interface Logic

Registers

UTOPIA Module

Local TDM Bus

32 x 64 kbps in /

32 x 64 kbps out

Clock

Recovery

MT90500

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90502 | Multi-Channel AAL2 SAR(多通道 ATM AAL2分段及重組設(shè)備(基于通訊總線的系統(tǒng)與ATM網(wǎng)絡(luò)的接口)) |

| MT90732AP | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90732 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90733 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90733AP | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90500AL-ENG1 | 制造商:Mitel Networks Corporation 功能描述: |

| MT90502 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-Channel AAL2 SAR |

| MT90502_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-Channel AAL2 SAR |

| MT90502AG | 制造商:Rochester Electronics LLC 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: |

| MT90503 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:2048VC AAL1 SAR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。