- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄369950 > PCI1520-EP Military Enhanced Plastic PC Card Controllers Data Manual PDF資料下載

參數(shù)資料

| 型號(hào): | PCI1520-EP |

| 英文描述: | Military Enhanced Plastic PC Card Controllers Data Manual |

| 中文描述: | 軍事增強(qiáng)塑料PC卡控制器數(shù)據(jù)手冊(cè) |

| 文件頁(yè)數(shù): | 118/125頁(yè) |

| 文件大小: | 716K |

| 代理商: | PCI1520-EP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)當(dāng)前第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)

6

–

7

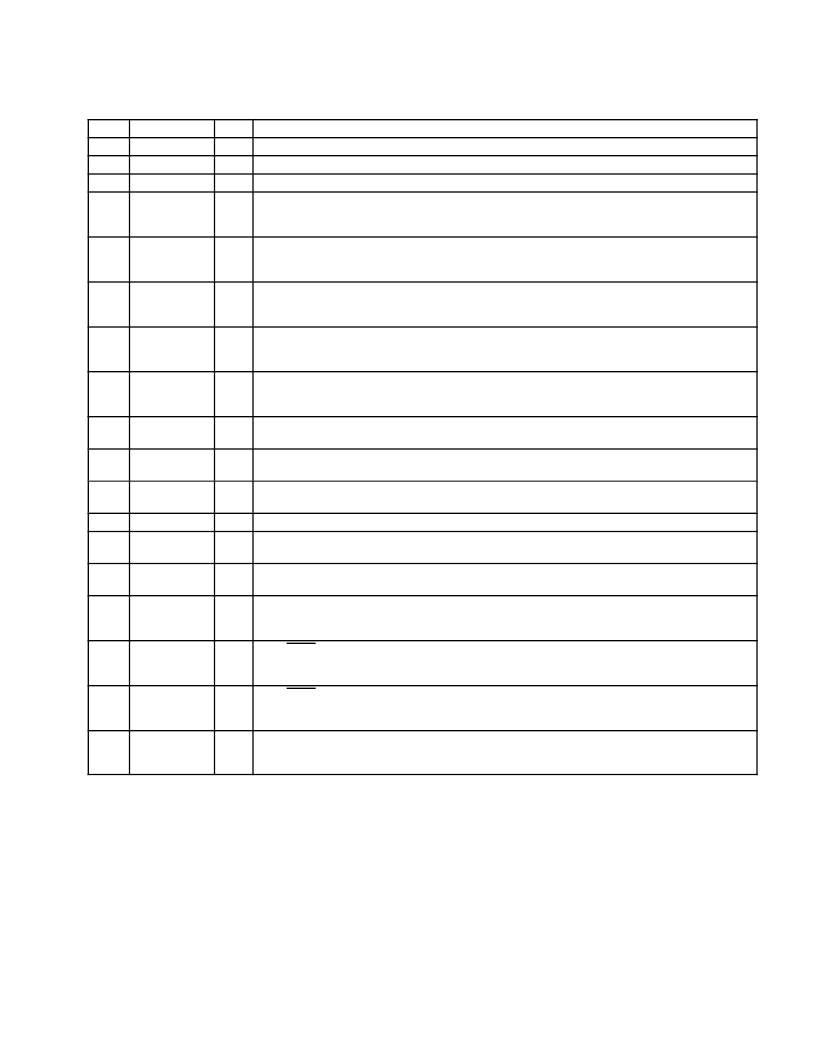

Table 6

–

5. Socket Force Event Register Description

BIT

SIGNAL

TYPE

FUNCTION

31

–

28

RSVD

R

Reserved. Bits 31

–

28 return 0s when read.

27

FZVSUPPORT

W

Zoomed-video support. This bit indicates whether or not the socket has support for zoomed video.

26

–

15

RSVD

R

Reserved. Bits 26

–

15 return 0s when read.

14

CVSTEST

W

Card VS test. When bit 14 is set, the PCI1520 re-interrogates the PC Card, updates the socket present-state

register (CB offset 08h, see Section 6.3), and enables the socket control register (CB offset 10h, see

Section 6.5).

13

FYVCARD

W

Force YV card. Write transactions to bit 13 cause bit 13 (YVCARD) in the socket present-state register (CB

offset 08h, see Section 6.3) to be written. When set, this bit disables the socket control register (CB offset

10h, see Section 6.5).

12

FXVCARD

W

Force XV card. Write transactions to bit 12 cause bit 12 (XVCARD) in the socket present-state register (CB

offset 08h, see Section 6.3) to be written. When set, this bit disables the socket control register (CB offset

10h, see Section 6.5).

11

F3VCARD

W

Force 3-V card. Write transactions to bit 11 cause bit 11 (3VCARD) in the socket present-state register (CB

offset 08h, see Section 6.3) to be written. When set, this bit disables the socket control register (CB offset

10h, see Section 6.5).

10

F5VCARD

W

Force 5-V card. Write transactions to bit 10 cause bit 10 (5VCARD) in the socket present-state register (CB

offset 08h, see Section 6.3) to be written. When set, this bit disables the socket control register (CB offset

10h, see Section 6.5).

9

FBADVCCREQ

W

Force bad VCC request. Changes to bit 9 (BADVCCREQ) in the socket present-state register (CB offset 08h,

see Section 6.3) can be made by writing to bit 9.

8

FDATALOST

W

Force data lost. Write transactions to bit 8 cause bit 8 (DATALOST) in the socket present-state register (CB

offset 08h, see Section 6.3) to be written.

7

FNOTACARD

W

Force not-a-card. Write transactions to bit 7 cause bit 7 (NOTACARD) in the socket present-state register

(CB offset 08h, see Section 6.3) to be written.

6

RSVD

R

Reserved. Bit 6 returns 0 when read.

5

FCBCARD

W

Force CardBus card. Write transactions to bit 5 cause bit 5 (CBCARD) in the socket present-state register

(CB offset 08h, see Section 6.3) to be written.

4

F16BITCARD

W

Force 16-bit card. Write transactions to bit 4 cause bit 4 (16BITCARD) in the socket present-state register

(CB offset 08h, see Section 6.3) to be written.

3

FPWRCYCLE

W

Force power cycle. Write transactions to bit 3 cause bit 3 (PWREVENT) in the socket event register (CB

offset 00h, see Section 6.1) to be written, and bit 3 (PWRCYCLE) in the socket present-state register (CB

offset 08h, see Section 6.3) is unaffected.

2

FCDETECT2

W

Force CCD2. Write transactions to bit 2 cause bit 2 (CD2EVENT) in the socket event register (CB offset 00h,

see Section 6.1) to be written, and bit 2 (CDETECT2) in the socket present-state register (CB offset 08h,

see Section 6.3) is unaffected.

1

FCDETECT1

W

Force CCD1. Write transactions to bit 1 cause bit 1 (CD1EVENT) in the socket event register (CB offset 00h,

see Section 6.1) to be written, and bit 1 (CDETECT1) in the socket present-state register (CB offset 08h,

see Section 6.3) is unaffected.

0

FCARDSTS

W

Force CSTSCHG. Write transactions to bit 0 cause bit 0 (CSTSEVENT) in the socket event register (CB

offset 00h, see Section 6.1) to be written, and bit 0 (CARDSTS) in the socket present-state register (CB

offset 08h, see Section 6.3) is unaffected.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI1620GHK | Controller Miscellaneous - Datasheet Reference |

| PCI1620PDV | Controller Miscellaneous - Datasheet Reference |

| PCI2050A | 32-Bit. 66MHz. 9-Master PCI-to-PCI Bridge |

| PCI2050GHK | BUS CONTROLLER |

| PCI2050PDV | BUS CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI1520GHK | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI PC CARD CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI1520I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PC CARD CONTROLLERS |

| PCI1520IGHK | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI PC CARD CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI1520IGHKEP | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI Mil Enhance PC Card Cntrlr Data Manual RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI1520IPDV | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI PC CARD CONTROLLER RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。