- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376464 > XRT86VL3x (Exar Corporation) Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號: | XRT86VL3x |

| 廠商: | Exar Corporation |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 93/153頁 |

| 文件大?。?/td> | 1316K |

| 代理商: | XRT86VL3X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當(dāng)前第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

XRT86VL3X

86

REV. 1.2.2

T1/E1/J1 FRAMER/LIU COMBO - ARCHITECTURE DESCRIPTION

In Extended Super-Frame framing mode, frame number 6, 12, 18 and 24 are signaling frames. In these

frames, the least significant bit of all twenty-four timeslots is 'robbed' to carry call state information. The bit in

frame 6 is called the A bit, the bit in frame 12 is called the B bit, the bit in frame 18 is called the C bit and the bit

in frame 24 is called the D bit. The combination of A, B, C and D defines the state of the call for the particular

timeslot that these signaling bits are located in.

8.3.1

Configure the framer to transmit Robbed-bit Signaling

The XRT86VL3x framer supports transmission of Robbed-bit Signaling in ESF, SF and SLC96 framing

formats. Signaling bits can be inserted into the outgoing DS1 frame through the following:

Signaling data is inserted from Transmit Signaling Control Registers (TSCR) of each timeslot

Signaling data is inserted from TxSig_n pin

Signaling data is embedded into the input PCM data coming from the Terminal Equipment

8.3.2

Insert Signaling Bits from TSCR Register

The four most significant bits of the Transmit Signaling Control Register (TSCR) of each timeslot can be used

to store outgoing signaling data. The user can program these bits through the microprocessor access. If the

XRT86VL3x framer is configured to insert signaling bits from the TSCR registers, the DS1 Transmit Framer

block will strip off the least significant bits of each time slot in the signaling frames and replace it with the

signaling bit stored inside the TSCR registers. The insertion of signaling bits into PCM data is done on a per-

channel basis.

In SF or SLC96 mode, the user can control the XRT86VL3x framer to transmit no signaling (transparent),

two-code signaling, or four-code signaling. Two-code signaling is done by substituting the least significant bit

(LSB) of the specific channel in frame 6 and 12 with the content of the Signaling bit A of the specific TSCR

register.

Four-code signaling is done by substituting the LSB of channel data in frame 6 with the Signaling bit A and the

LSB of channel data in frame 12 with the Signaling bit B of the specific channel's TSCR register. If sixteen-code

signaling is selected in SF format, only the Signaling bit A and Signaling bit B information are used.

In ESF mode, the user can control the XRT86VL3x framer to transmit no signaling (transparent) by disable

signaling insertion, two-code signaling, four-code signaling or sixteen code signaling. Two-code signaling is

done by substituting the least significant bit (LSB) of the specific channel in frame 6, 12, 18 and 24 with the

content of the Signaling bit A of the specific TSCR register.

Four-code signaling is done by substituting the LSB of channel data in frame 6 and frame 18 with the Signaling

bit A and the LSB of channel data in frame 12 and frame 24 with the Signaling bit B of the specific channel's

TSCR register.

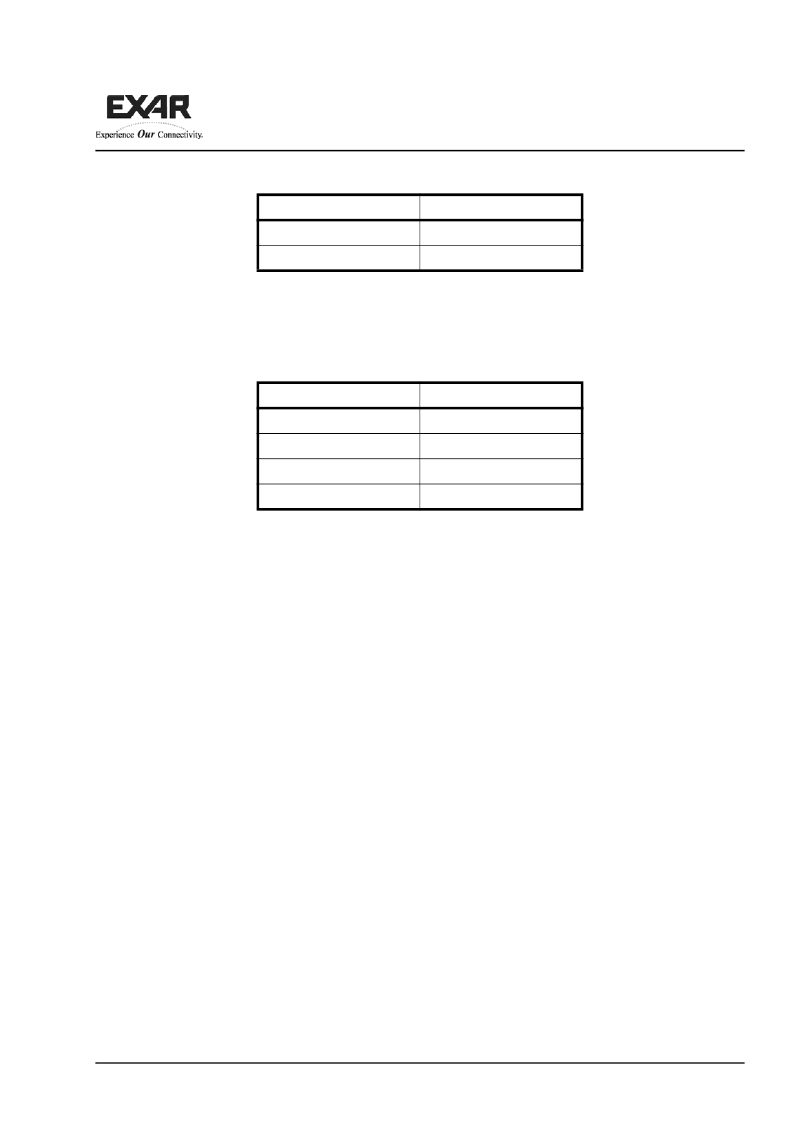

F

RAME

N

UMBER

S

IGNALING

B

IT

6

A

12

B

F

RAME

N

UMBER

S

IGNALING

B

IT

6

A

12

B

18

C

24

D

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT86VL3X_07 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| XRT86VL3X | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| XRT91L30_0611 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L306 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30IQ | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT86VL3X_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:T1/E1/J1 FRAMER/LIU COMBO - ARCHITECTURE DESCRIPTION |

| XRT86VL3X_0710 | 制造商:EXAR 制造商全稱:EXAR 功能描述:T1/E1/J1 FRAMER/LIU COMBO - ARCHITECTURE DESCRIPTION |

| XRT86VX38 | 制造商:EXAR 制造商全稱:EXAR 功能描述:OCTAL T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION |

| XRT86VX38_09 | 制造商:EXAR 制造商全稱:EXAR 功能描述:8-CHANNEL T1/E1/J1 FRAMER/LIU COMBO - T1 REGISTER DESCRIPTION |

| XRT86VX38_0906 | 制造商:EXAR 制造商全稱:EXAR 功能描述:OCTAL T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。