- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄358620 > 30046-23 (NATIONAL SEMICONDUCTOR CORP) Low Power Integrated x86-Compatible 32-Bit Geode GXLV Processor(低功耗集成兼容X86的32位 Geode GXLV技術(shù)處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | 30046-23 |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | Low Power Integrated x86-Compatible 32-Bit Geode GXLV Processor(低功耗集成兼容X86的32位 Geode GXLV技術(shù)處理器) |

| 中文描述: | 32-BIT, 200 MHz, MICROPROCESSOR, CPGA320 |

| 封裝: | SPGA-320 |

| 文件頁(yè)數(shù): | 235/247頁(yè) |

| 文件大小: | 4379K |

| 代理商: | 30046-23 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)第234頁(yè)當(dāng)前第235頁(yè)第236頁(yè)第237頁(yè)第238頁(yè)第239頁(yè)第240頁(yè)第241頁(yè)第242頁(yè)第243頁(yè)第244頁(yè)第245頁(yè)第246頁(yè)第247頁(yè)

Revision 1.2

235

www.national.com

Instruction Set (

Continued

)

G

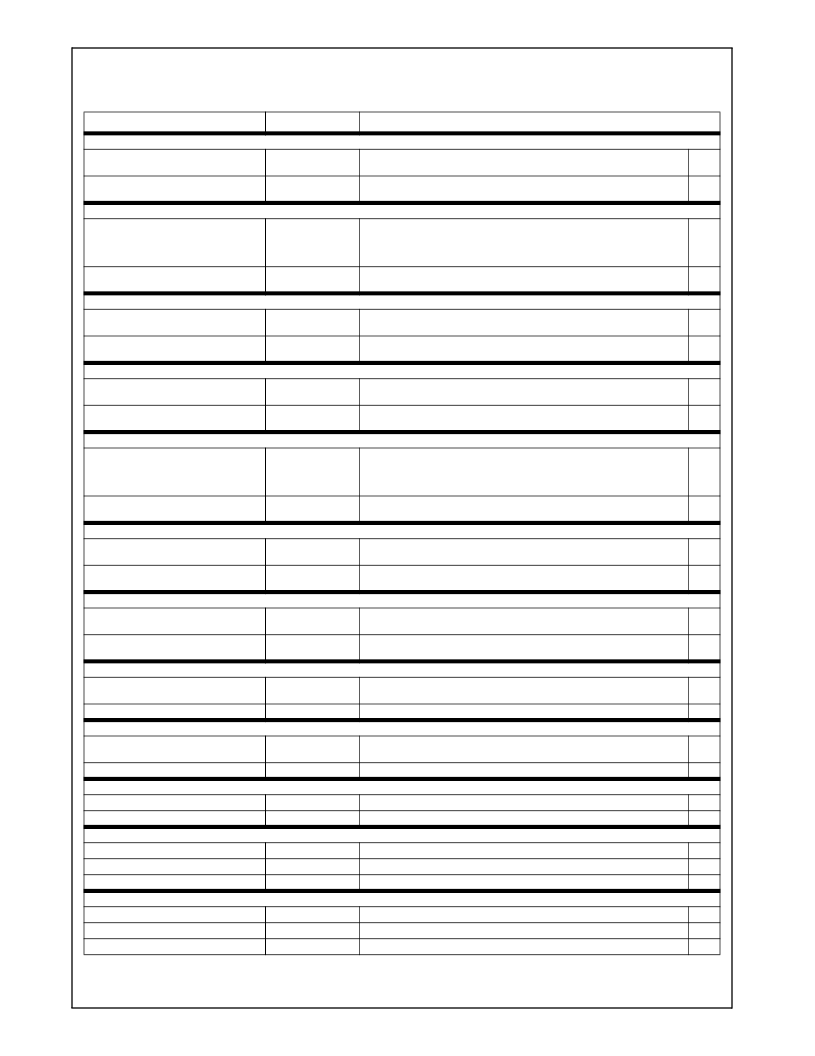

PCMPEQB

Packed Byte Compare for Equality

MMX Register 2 with MMX Register 1

0F74 [11 mm1 mm2]

MMX reg 1 [byte] <--FFh-- if MMX reg 1 [byte] = MMX reg 2 [byte]

MMX reg 1 [byte]<--00h-- if MMX reg 1 [byte] NOT = MMX reg 2 [byte]

1/1

Memory with MMX Register

0F74 [mod mm r/m]

MMX reg [byte] <--FFh-- if memory[byte] = MMX reg [byte]

MMX reg [byte] <--00h-- if memory[byte] NOT = MMX reg [byte]

1/1

PCMPEQD

Packed Dword Compare for Equality

MMX Register 2 with MMX Register 1

0F76 [11 mm1 mm2]

MMX reg 1 [dword] <--FFFF FFFFh-- if MMX reg 1 [dword] = MMX reg 2

[dword]

MMX reg 1 [dword]<--0000 0000h--if MMX reg 1[dword] NOT = MMX reg 2

[dword]

1/1

Memory with MMX Register

0F76 [mod mm r/m]

MMX reg [dword] <--FFFF FFFFh-- if memory[dword] = MMX reg [dword]

MMX reg [dword] <--0000 0000h-- if memory[dword] NOT = MMX reg [dword]

1/1

PCMPEQW

Packed Word Compare for Equality

MMX Register 2 with MMX Register 1

0F75 [11 mm1 mm2]

MMX reg 1 [word] <--FFFFh-- if MMX reg 1 [word] = MMX reg 2 [word]

MMX reg 1 [word]<--0000h-- if MMX reg 1 [word] NOT = MMX reg 2 [word]

1/1

Memory with MMX Register

0F75 [mod mm r/m]

MMX reg [word] <--FFFFh-- if memory[word] = MMX reg [word]

MMX reg [word] <--0000h-- if memory[word] NOT = MMX reg [word]

1/1

PCMPGTB

Pack Compare Greater Than Byte

MMX Register 2 to MMX Register 1

0F64 [11 mm1 mm2]

MMX reg 1 [byte] <--FFh-- if MMX reg 1 [byte] > MMX reg 2 [byte]

MMX reg 1 [byte]<--00h-- if MMX reg 1 [byte] NOT > MMX reg 2 [byte]

1/1

Memory with MMX Register

0F64 [mod mm r/m]

MMX reg [byte] <--FFh-- if memory[byte] > MMX reg [byte]

MMX reg [byte] <--00h-- if memory[byte] NOT > MMX reg [byte]

1/1

PCMPGTD

Pack Compare Greater Than Dword

MMX Register 2 to MMX Register 1

0F66 [11 mm1 mm2]

MMX reg 1 [dword] <--FFFF FFFFh-- if MMX reg 1 [dword] > MMX reg 2

[dword]

MMX reg 1 [dword]<--0000 0000h--if MMX reg 1 [dword]NOT > MMX reg 2

[dword]

1/1

Memory with MMX Register

0F66 [mod mm r/m]

MMX reg [dword] <--FFFF FFFFh-- if memory[dword] > MMX reg [dword]

MMX reg [dword] <--0000 0000h-- if memory[dword] NOT > MMX reg [dword]

1/1

PCMPGTW

Pack Compare Greater Than Word

MMX Register 2 to MMX Register 1

0F65 [11 mm1 mm2]

MMX reg 1 [word] <--FFFFh-- if MMX reg 1 [word] > MMX reg 2 [word]

MMX reg 1 [word]<--0000h-- if MMX reg 1 [word] NOT > MMX reg 2 [word]

1/1

Memory with MMX Register

0F65 [mod mm r/m]

MMX reg [word] <--FFFFh-- if memory[word] > MMX reg [word]

MMX reg [word] <--0000h-- if memory[word] NOT > MMX reg [word]

1/1

PMADDWD

Packed Multiply and Add

MMX Register 2 to MMX Register 1

0FF5 [11 mm1 mm2] MMX reg 1 [dword] <--add-- [dword]<---- MMX reg 1 [sign word]*MMX reg

2[sign word]

2/1

Memory to MMX Register

0FF5 [mod mm r/m]

MMX reg 1 [dword] <--add-- [dword] <---- memory [sign word] * Memory [sign

word]

2/1

PMULHW

Packed Multiply High

MMX Register 2 to MMX Register 1

0FE5 [11 mm1 mm2] MMX reg 1 [word] <--upper bits-- MMX reg 1 [sign word] * MMX reg 2 [sign

word]

2/1

Memory to MMX Register

0FE5 [mod mm r/m]

MMX reg 1 [word] <--upper bits-- memory [sign word] * Memory [sign word]

2/1

PMULLW

Packed Multiply Low

MMX Register 2 to MMX Register 1

0FD5 [11 mm1 mm2] MMX reg 1 [word] <--lower bits-- MMX reg 1 [sign word] * MMX reg 2 [sign

word]

2/1

Memory to MMX Register

0FD5 [mod mm r/m]

MMX reg 1 [word] <--lower bits-- memory [sign word] * Memory [sign word]

2/1

POR

Bitwise OR

MMX Register 2 to MMX Register 1

0FEB [11 mm1 mm2] MMX reg 1 [qword] <--logic OR-- MMX reg 1 [qword], MMX reg 2 [qword]

1/1

Memory to MMX Register

0FEB [mod mm r/m]

MMX reg [qword] <--logic OR-- MMX reg [qword], memory[qword]

1/1

PSLLD

Packed Shift Left Logical Dword

MMX Register 1 by MMX Register 2

0FF2 [11 mm1 mm2] MMX reg 1 [dword] <--shift left, shifting in zeroes by MMX reg 2 [dword]--

1/1

MMX Register by Memory

0FF2 [mod mm r/m]

MMX reg [dword] <--shift left, shifting in zeroes by memory[dword]--

1/1

MMX Register by Immediate

0F72 [11 110 mm] #

MMX reg [dword] <--shift left, shifting in zeroes by [im byte]--

1/1

PSLLQ

Packed Shift Left Logical Qword

MMX Register 1 by MMX Register 2

0FF3 [11 mm1 mm2] MMX reg 1 [qword] <--shift left, shifting in zeroes by MMX reg 2 [qword]--

1/1

MMX Register by Memory

0FF3 [mod mm r/m]

MMX reg [qword] <--shift left, shifting in zeroes by [qword]--

1/1

MMX Register by Immediate

0F73 [11 110 mm] #

MMX reg [qword] <--shift left, shifting in zeroes by [im byte]--

1/1

Table 7-31. MMX Instruction Set Summary (Continued)

MMX Instructions

Opcode

Operation and Clock Count (Latency/Throughput)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 300471U | Radial, -55dotc, long life wsitching-power |

| 300CNQ | SCHOTTKY RECTIFIER |

| 300CNQ035 | SCHOTTKY RECTIFIER |

| 300CNQ040 | SCHOTTKY RECTIFIER |

| 300CNQ045 | SCHOTTKY RECTIFIER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 30046-46L | 制造商:LENOX 功能描述:HOLE SAW BI-METAL 73MM |

| 300-466A | 制造商:LG Corporation 功能描述:CABINET ASSYCMT-9325 |

| 300-466B | 制造商:LG Corporation 功能描述:CABINET ASSYCMT-9324 |

| 300-466K | 制造商:LG Corporation 功能描述:CABINET ASSYCMT-9322 |

| 300-466R | 制造商:LG Corporation 功能描述:FRONT CABINET |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。