- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16169 > 78Q8430-ARM9-EVM (Maxim Integrated Products)EVALUATION MODULE 78Q8430 ARM9 PDF資料下載

參數(shù)資料

| 型號(hào): | 78Q8430-ARM9-EVM |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 21/88頁(yè) |

| 文件大小: | 0K |

| 描述: | EVALUATION MODULE 78Q8430 ARM9 |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)

78Q8430 Data Sheet

DS_8430_001

28

Rev. 1.2

6.3.2.1

Using the Setup Transmit Data Register

The Setup Transmit Data Register (STDR) can be used to control the way in which 32-bit data words are

transferred to the transmit FIFO. The STDR can be changed on a word-by-word basis to change the

network endianness or buffer-byte-alignment, or the STDR can be used to setup the transfer of an entire

buffer of transmit data. A new frame must be initialized by a write to the PCWR before the STDR is setup

for transferring frame data to the QUE.

The Count field of the STDR contains one less than the number of writes to the TDR that will be needed

to complete the transfer of the buffer. The Start Offset field contains the number of bytes in the first write

to the TDR to ignore. The End Offset field contains the number of bytes in the last write (when the Count

field is equal to zero) to ignore.

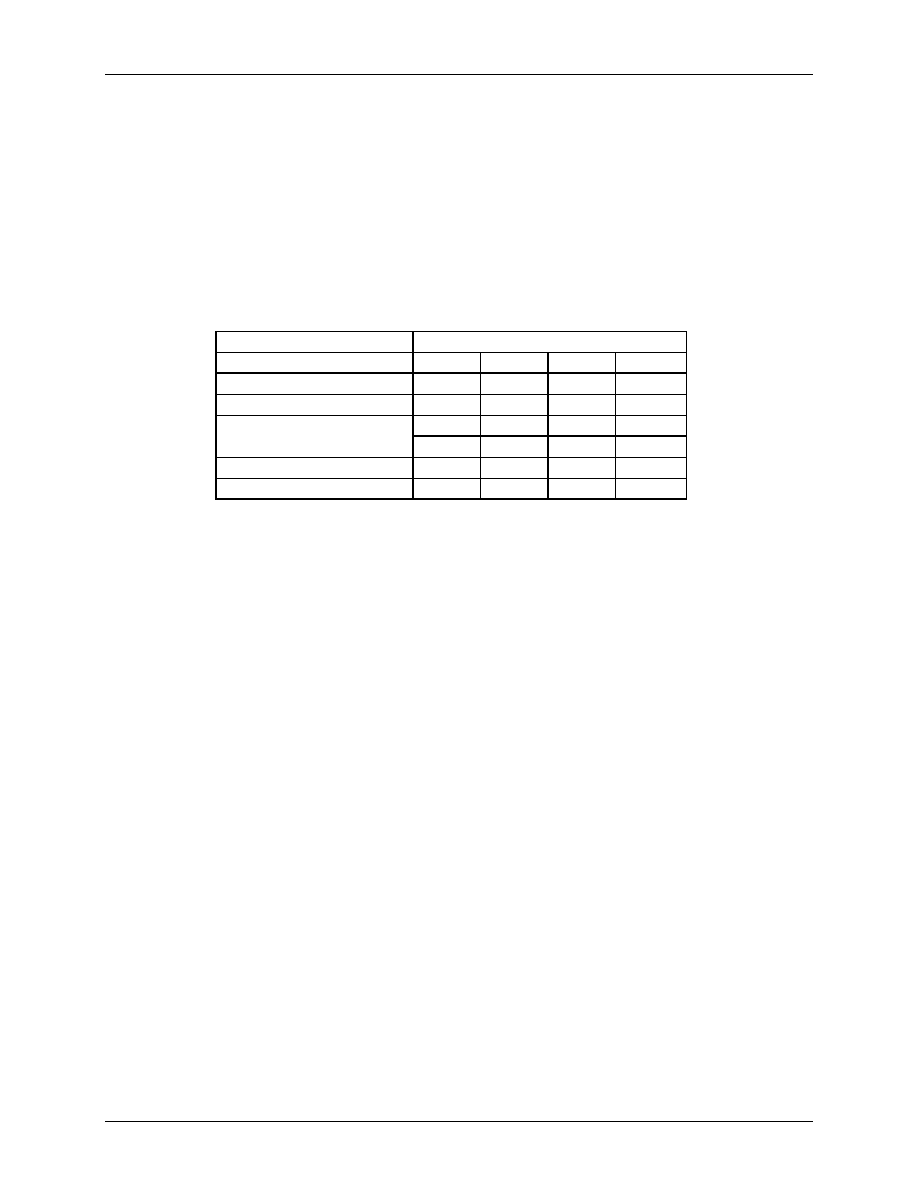

Table 22: Transmit Data Buffer Example

32-bit Write Data

Transmit Order:

Byte-1

Byte-2

Byte-3

Byte-4

Start Offset = 2

X

B1

B2

B3

B4

B5

B6

Count decrements for

each write

…

B

N-4

B

N-3

B

N-2

N-1

End Offset = 3

B

X

N

X

Notes:

1.

The End Offset will continue to be applied as long as the COUNT field of the STDR contains zero. If

a non-zero End Offset is used, it must be cleared at the end of the block transfer.

2.

The COUNT field must expire before the PSZR expires. Frames that are entirely contained within

The Endian field of the STDR is used to set the transmit order of the data written on the bus, or how host

bus write data bytes are mapped to transmit buffer bytes. If the Endian bit is set then the most significant

byte of the host bus as defined by the logical endianness, is mapped to the first transmitted byte in the

buffer, otherwise, the least significant byte is mapped to the first transmitted byte.

6.3.2.2

Preloading Transmit Data

A transmit QUE signals the MAC transmitter that it is ready to transmit by asserting the QUE Data Ready

bit (QDR) in its QUE Status Register (QSR). The default behavior of the QDR for a transmit QUE is to

assert anytime the QUE contains any data. This means that a transmit QUE can potentially begin

transmitting as soon as the first BLOCK is added to the QUE. Once the QUE begins transmitting, data for

the packet being transmitted must be added to the QUE faster than the transmitter removes it or a TX

FIFO under-run condition will eventually abort the packet (see TPSR).

In the event that interrupt latency, host bus performance, or other issues may prevent the host from

loading data into the QUE faster than it is removed by the MAC, the QSR can be used to modify the QDR

behavior and prevent an under-run condition on the QUE. Bits 25 and 24 of the QSR are the Mode field.

The default setting for the Mode field is 00b. In this mode the QDR bit is set anytime the QUE contains at

least one BLOCK. In this mode, the host must be diligent in keeping the QUE populated with data to

avoid a TX FIFO under-run condition in the MAC.

If the Mode setting is 01b then the QDR bit for the QUE is set only when the number of BLOCKs in the

QUE is above the value indicated by the Threshold field. This will allow the host to fill the QUE up to the

threshold level at its leisure without risk of a TX FIFO under-run. The drawback to this mode is that a

small packet that uses fewer than the threshold number of BLOCKs will be stranded in the QUE until

more data is added to the QUE to bring the total number of BLOCKs up and over the threshold.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-24T-EY-S | CONVERTER MOD DC/DC 6.5V 50W |

| M1YXK-2640K | IDC CABLE - MPD26K/MC26F/X |

| 382LX392M200N082 | CAP ALUM 3900UF 200V 20% SNAP |

| M3DEK-2606R | IDC CABLE - MKR26K/MC26M/MCE26K |

| ECM30DCBD-S189 | CONN EDGECARD 60POS R/A .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 78Q8430EBST#DB | 功能描述:以太網(wǎng)開發(fā)工具 3-in-1 Silicon Delay Line RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類型:RMII 工作電源電壓: |

| 78Q8430STEM#DB | 功能描述:以太網(wǎng)開發(fā)工具 3-in-1 Silicon Delay Line RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類型:RMII 工作電源電壓: |

| 78-R3 | 功能描述:3M SCOTCHCAST REENTERABLE SIGNAL 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 78-R4 | 功能描述:3M SCOTCHCAST REENTERABLE SIGNAL 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 78RB02 | 功能描述:SWITCH 2 POS DIP RECESSED UNSLD RoHS:否 類別:開關(guān) >> DIP 系列:78 特色產(chǎn)品:RDM Series Rotary DIP Switch 標(biāo)準(zhǔn)包裝:70 系列:RDM 電路:十六進(jìn)制 位置數(shù):16 觸點(diǎn)額定電壓:0.1A @ 42VDC 觸動(dòng)器類型:用于工具旋轉(zhuǎn) 觸動(dòng)器電平:凹槽式 安裝類型:通孔 方向:頂部觸動(dòng) 可清洗:是 其它名稱:EG4977-5RDMAR16PIT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。