- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6635BB (ANALOG DEVICES INC) 4-Channel, 80 MSPS WCDMA Receive Signal Processor (RSP) PDF資料下載

參數(shù)資料

| 型號: | AD6635BB |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 無繩電話/電話 |

| 英文描述: | 4-Channel, 80 MSPS WCDMA Receive Signal Processor (RSP) |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PBGA324 |

| 封裝: | 19 X 19 MM, PLASTIC, BGA-324 |

| 文件頁數(shù): | 45/60頁 |

| 文件大?。?/td> | 799K |

| 代理商: | AD6635BB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

REV. 0

AD6635

–45–

0xA4: RCF Control Register

The RCF control register is an 11-bit register that controls

general features of the RCF as well as output formatting. The

bits of this register and their functions are described below.

Bit 10 bypasses the RCF filter and sends the CIC5 output data

to the BIST-I and BIST-Q registers. The 16 MSBs of the CIC5

data can be accessed from this register if Bit 9 of the RCF con-

trol register 2 at channel address 0xA9 is set.

Bit 9 of this register controls the source of the input data to the

RCF. If this bit is 0, the RCF processes the output data of its

own channel. If this bit is 1, it processes the data from the

CIC5 of another channel. Table XII shows which CIC5 the

RCF is connected to when this bit is 1. These can be used to

allow multiple RCFs to be used together to process wider band-

width channels.

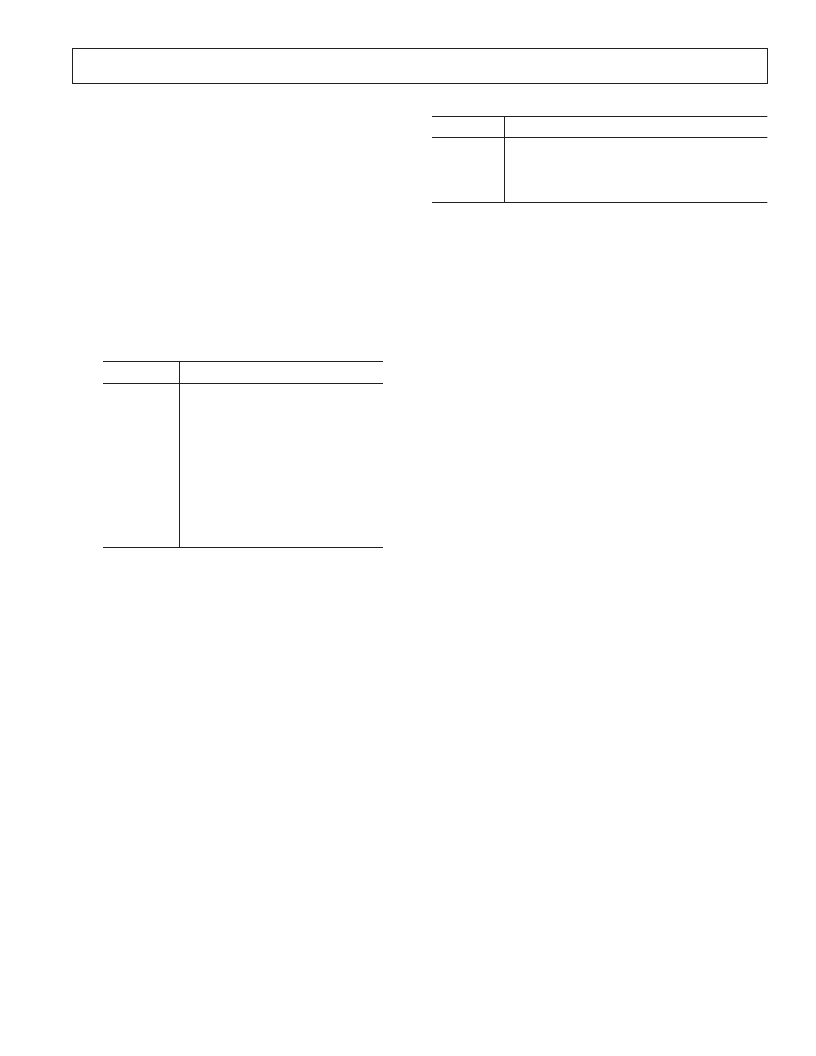

Table XII. RCF Input Configurations

Channel

RCF Input Source when Bit 9 is 1

0

1

2

3

4

5

6

7

1

0

1

1

5

4

5

5

Bit 8 is used as an extra address to allow a second block of 128

words of CMEM to be addressed by the channel addresses at

0x00–0x7F. If this bit is 0, the first 128 words are written; and

if this bit is 1, a second 128 words are written. This bit is only

used to program the coefficient memory. It is not used in

any way by the processing, and filters longer than 128 taps

can be performed.

Bit 7 is used to help control the output formatting of the

AD6635’s RCF data. This bit is only used when the 8 + 4 or

12 + 4 floating-point modes are chosen. These modes are

enabled by Bits 5 and 4 of this register. When Bit 7 is 0, the I

and Q output exponents are determined separately based on

their individual magnitudes. When this bit is 1, the I and Q

data is a complex floating-point number where I and Q use a

single exponent that is determined based on the maximum

magnitude of I or Q.

Bit 6 is used to force the output scale factor in Bits 3–0 of this

register to be used to scale the data even when one of the float-

ing point output modes is used. If the number was too large to

represent with the output scale chosen, the mantissas of the I

and Q data clip and do not overflow.

Bits 5 and 4 choose the output formatting option used by the

RCF data. The options are defined in Table XIII. The user

should note that these options are valid only when data is out-

put from the channels (by writing 0 into Bit 0 of parallel A/B

control register or link A/B control register). The output format

when data comes from AGCs is always fixed point with the bit

width defined by the AGC.

Table XIII. Output Formats

Bit Values

Output Option

1x

01

00

12-Bit Mantissa and 4-Bit Exponent (12 + 4)

8-Bit Mantissa and 4-Bit Exponent (8 + 4)

Fixed-Point Mode

Bits 3–0 of this register represent the output scale factor of the

RCF. This is used to scale the data when the output format is in

fixed-point mode or when the force exponent bit is high.

0xA5: BIST Register for I

This register serves two purposes. The first is to allow the com-

plete functionality of the I data path in the channel to be tested

in the system. Consult the User Configurable Built-in Self Test

(BIST) section for further details. The second function is to

provide access to the I output data through the microport. To

accomplish this, the Map RCF Data to BIST bit in the RCF

Control register 2, 0xA9 should be set high. 16 bits of I data can

then be read through the microport in either the 8 + 4, 12 + 4,

12–bit linear, or 16-bit linear output modes. This data may come

from either the formatted RCF output or the CIC5 output.

0xA6: BIST Register for Q

This register serves two purposes. The first is to allow the com-

plete functionality of Q data path in the channel to be tested in

the system. Consult the User Configurable Built-in self Test

(BIST) section for further details. The second function is to

provide access to the Q output data through the microport. To

accomplish this, the Map RCF Data to BIST bit in the RCF

control register 2, 0xA9 should be set high. 16 bits of Q data can

then be read through the microport in either the 8 + 4, 12 + 4,

12-bit linear, or 16-bit linear output modes. This data may

come from either the formatted RCF output or the CIC5 output.

0xA7: BIST Control Register

This register controls the number of outputs of the RCF or CIC

filter that are observed when a BIST test is performed. The

BIST signature registers at addresses 0xA5 and 0xA6 observe

this number of outputs and then terminate. The loading of this

register also starts the BIST engine running. Details of how to

utilize the BIST circuitry are defined in the User Configurable

Built-in Self Test (BIST) section.

0xA8: RAM BIST Control Register

This register is used to test the memories of the AD6635,

should they ever be suspected of a failure. Bit 0 of this register is

written with a 1 when the channel is in SLEEP, and the user

waits for 1600 CLKs and then polls the bits. If Bit 1 is high, the

CMEM failed the test; and if Bit 2 is high, the data memory

used by the RCF failed the test.

0xA9: Output Control Register

Bit 9 of this register allows the RCF or CIC5 data to be mapped

to the BIST registers at addresses 0xA5 and 0xA6. When this

bit is 0, the BIST register is in signature mode and ready for a

self test to be run. When this bit is 1, the output data from the

RCF––after formatting or the CIC5 data––is mapped to these

registers and can be read through the microport.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6636 | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636BBCZ1 | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636BC | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636CBCZ1 | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636PCB | 150 MSPS Wideband Digital Down-Converter (DDC) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6635BB/PCB | 制造商:Analog Devices 功能描述:Evaluation Kit For 4-Channel, 80MSPS WCDMA Receive Signal Processor |

| AD6635BBZ | 制造商:Analog Devices 功能描述:Receive Signal Processor 324-Pin BGA |

| AD6636 | 制造商:AD 制造商全稱:Analog Devices 功能描述:150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636BBC | 制造商:Analog Devices 功能描述:Digital Down Converter 256-Pin CSP-BGA |

| AD6636BBCZ | 功能描述:IC DIGITAL DWNCONV 6CH 256CSPBGA RoHS:是 類別:RF/IF 和 RFID >> RF 混頻器 系列:AD6636 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:100 系列:- RF 型:W-CDMA 頻率:2.11GHz ~ 2.17GHz 混頻器數(shù)目:1 增益:17dB 噪音數(shù)據(jù):2.2dB 次要屬性:- 電流 - 電源:11.7mA 電源電壓:2.7 V ~ 3.3 V 包裝:托盤 封裝/外殼:12-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:12-QFN-EP(3x3) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。