- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6636CBCZ1 (Analog Devices, Inc.) 150 MSPS Wideband Digital Down-Converter (DDC) PDF資料下載

參數(shù)資料

| 型號: | AD6636CBCZ1 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 數(shù)字上/下變頻 |

| 英文描述: | 150 MSPS Wideband Digital Down-Converter (DDC) |

| 中文描述: | 150MSPS的寬帶數(shù)字下變頻器(DDC) |

| 文件頁數(shù): | 24/72頁 |

| 文件大小: | 1629K |

| 代理商: | AD6636CBCZ1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

AD6636

Additional Control Bits

For additional flexibility in the power monitoring process, two

control bits are provided in the power-monitor control register.

The two control bits are the disable monitor period timer bit

and the clear-on-read bit. These options have the same function

in all three modes of operation.

Rev. 0 | Page 24 of 72

Disable Monitor Period Timer Bit

When the disable monitor period timer bit is written with

Logic 1, the timer continues to run but does not cause the

contents of the MSR to be transferred to the holding register

when the count reaches 1. This function of transferring the

MSR to the power monitor holding register and resetting the

MSR is now controlled by a read operation on the microport or

serial port.

When a microport or serial port read is performed on the

power monitor holding register, the MSR value is transferred to

the holding register. After the read operation, the timer is

reloaded with the AMPR value. If the timer reaches 1 before the

microport or serial port read, the MSR value is not transferred

to the holding register, as in normal operation. The timer still

generates an interrupt on the AD6636 interrupt pin and updates

the interrupt status register. An interrupt appears on the IRP

pin, if interrupts are enabled in the interrupt enable register.

Clear-on-Read Bit

This control bit is valid only when the disable monitor period

timer bit is Logic 1. When both of these bits are set, a read

operation to either the microport or the serial port reads the

MSR value and the monitor period timer is reloaded with the

AMPR value. The MSR is cleared (written with current input

signal magnitude in peak power and mean power mode; written

with a zero in threshold crossing mode), and normal operation

continues.

When the monitor period timer is disabled and the clear-on-

read bit is set, a read operation to the power monitor holding

register clears the contents of the MSR and, therefore, the power

monitor loop restarts.

If the clear-on-read bit is Logic 0, the read operation to the

microport or serial port does not clear the MSR value after it is

transferred into the holding register. The value from the

previous monitor time period persists, and it continues to be

compared, accumulated, or incremented, based on new input

signal magnitude values.

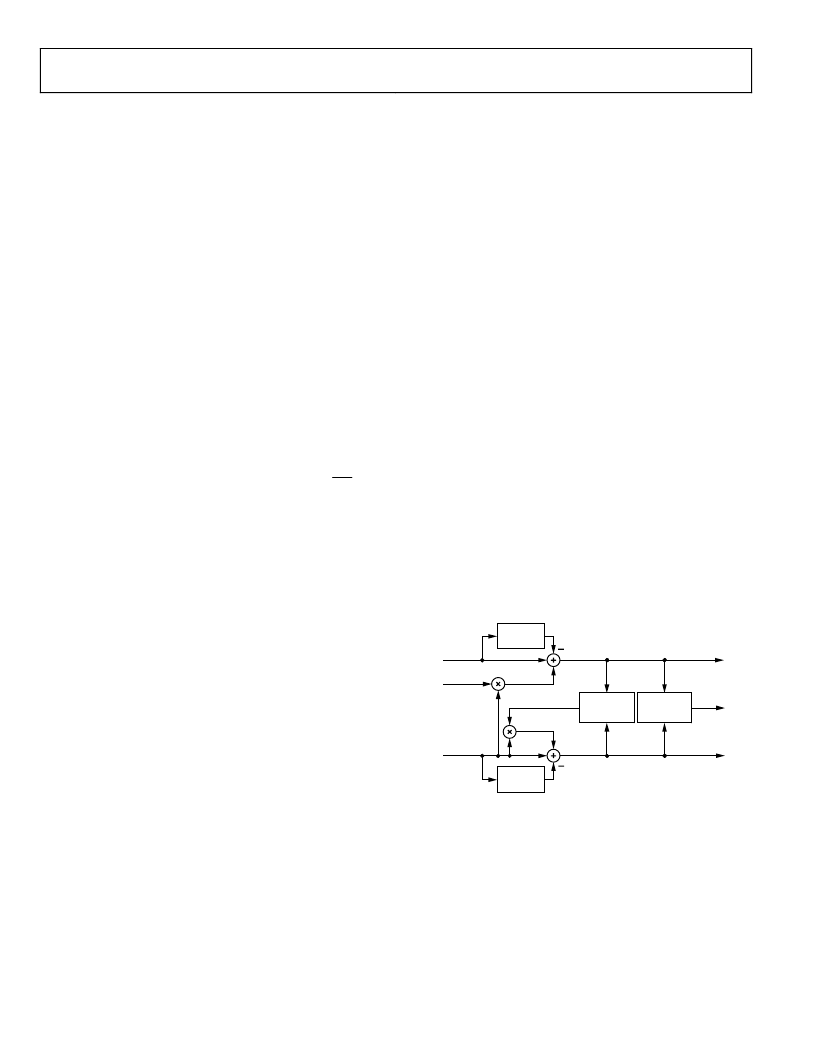

QUADRATURE I/Q CORRECTION BLOCK

When the I and Q paths are digitized using separate ADCs, as in

quadrature IF down-conversion, a mismatch often occurs

between I and Q due to variations in the ADCs from the

manufacturing process. The AD6636 is equipped with two

quadrature correction blocks that can be used to correct I/Q

mismatch errors in a complex baseband input stream. These I/Q

mismatches can result in spectral distortions, and removing

them is useful.

Two such blocks are present, one each for the I/Q signal formed

by combining the A and B inputs and the C and D inputs,

respectively. The I/Q correction block can be enabled when the

Port A (or Port C) complex data active bit is enabled in the

ADC input control register. This block is bypassed when real

input data is present on the ADC input ports, because there is

no possibility of I/Q mismatch in real data.

The I/Q or quadrature correction block consists of three

independent subblocks: dc correction, phase correction, and

amplitude correction. Three individual bits in the AB (or CD)

correction control registers can be used to enable or disable

each of these subblocks independently. Figure 29 shows the

contents and definitions of the registers related to the

quadrature correction block.

DC

ESTIMATE

DC

ESTIMATE

MAGNITUDE

ERROR

ESTIMATION

PHASE ESTIMATE

[13:0]

PHASE

ESTIMATE

[13:0]

Q_OUT [15:0]

TO NEXT BLOCK

I_OUT [15:0]

TO NEXT BLOCK

I [15:0] FROM

INPUT PORT

Q [15:0] FROM

INPUT PORT

0

PHASE

ERROR

ESTIMATION

MAGNITUDE

ESTIMATE [13:0]

Figure 29. Quadrature Correction Block Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6636PCB | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD664(中文) | Monolithic 12-Bit Quad DAC(單片12位四D/A轉(zhuǎn)換器) |

| AD6640 | 12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640AST | 12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640PCB | 12-Bit, 65 MSPS IF Sampling A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6636PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636XBCZ | 制造商:Analog Devices 功能描述: |

| AD664 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Monolithic 12-Bit Quad DAC |

| AD6640 | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640AST | 制造商:Analog Devices 功能描述:ADC Single Pipelined 65Msps 12-bit Parallel 44-Pin LQFP 制造商:Analog Devices 功能描述:ADC SGL PIPELINED 65MSPS 12-BIT PARALLEL 44LQFP - Trays 制造商:Rochester Electronics LLC 功能描述:12-BIT 65 MSPS MONOLITHIC A/D CONVERTER - Tape and Reel 制造商:Analog Devices 功能描述:Analog-Digital Converter IC Number of Bi |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。