- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6636CBCZ1 (Analog Devices, Inc.) 150 MSPS Wideband Digital Down-Converter (DDC) PDF資料下載

參數(shù)資料

| 型號: | AD6636CBCZ1 |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 數(shù)字上/下變頻 |

| 英文描述: | 150 MSPS Wideband Digital Down-Converter (DDC) |

| 中文描述: | 150MSPS的寬帶數(shù)字下變頻器(DDC) |

| 文件頁數(shù): | 70/72頁 |

| 文件大小: | 1629K |

| 代理商: | AD6636CBCZ1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當前第70頁第71頁第72頁

AD6636

DESIGN NOTES

The following guidelines describe circuit connections, layout

requirements, and programming procedures for the AD6636.

The designer should review these guidelines before starting the

system design and layout.

Rev. 0 | Page 70 of 72

The AD6636 requires the following power-up sequence: The

VDDCORE (1.8 V) must settle into nominal voltage levels

before the VDDIO attains the minimum. This ensures that,

on power-up, the JTAG does not take control of the I/O

pins.

Input clocks (CLKA, CLKB, CLKC, CLKD) and input port

pins (INA[15:0] to IND[15:0], EXPA[2:0] to EXPD[2:0]) are

not 5 V tolerant. Care should be taken to drive these pins

within the limits of VDDIO (3.0 V to 3.6 V).

When the ADC output has less than 16 bits of resolution,

it should be connected to the MSBs of the input port (MSB-

justified). The remaining LSBs should be connected to

ground.

The number format used in this part is twos complement.

All input ports and output ports use twos complement data

format. The formats for individual internal registers are

given in the memory map description of these registers.

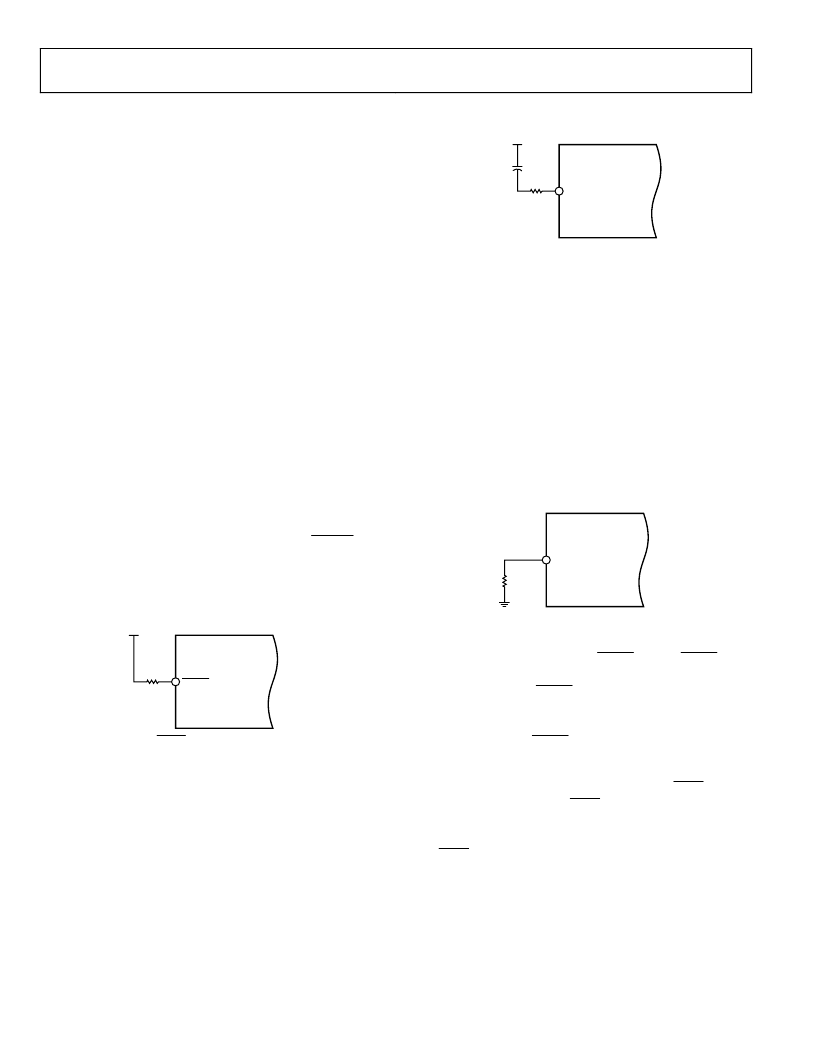

In both microport and serial port operation, the DTACK

(RDY, SDO) pin is an open-drain output and, therefore,

should be pulled high externally using a pull-up resister.

The recommended value for the pull-up resistor is from

1 k and 5 k.

0

DTACK (RDY, SDO)

AD6636

1k

3.3V

Figure 50. DTACK, SDO Pull-Up Resistor Circuit

A simple RC circuit is used on the EXT_FILTER pin to

balance the internal RC circuit on this pin and maintain a

good PLL clock lock. The recommended circuit is shown in

Figure 51, with the RC circuit connected to VDDCORE.

This RC circuit should be placed as close as possible to the

AD6636 part. This layout ensures that the PLL clock is void

of noise and spurs and the PLL lock is maintained closely.

0

EXT_FILTER

AD6636

10k

VDDCORE (1.8V)

0.01

μ

F

Figure 51. EXT_FILTER Circuit for PLL Clock

By default, the PLL CLK is disabled. It can be enabled by

programming the PLL multiplier and divider bits in the

ADC CLK control register. When the PLL CLK is enabled

by programming this register, it takes about 50 to 200 μs to

settle down. While the PLL loop settles down, the voltage at

the EXT_FILTER pin increases from 0 V to VDDCORE (1.8

V) and settles there. Channel registers and output port

registers (Addresses 0x68 to 0xE7) should not be pro-

grammed before the PLL loop settles down.

The LVDS_RSET pin is used to calibrate the current in the

LVDS pads. The recommended circuit for this pin is shown

in Figure 52. This resistor should be placed as close as

possible to the AD6636 part. This resistor is not required, if

CMOS mode input is used.

0

LVDS_RSET

AD6636

10k

Figure 52. LVDS_RSET Circuit for LVDS Calibration

To reset the AD6636 part, the user needs to provide a

minimum pulse of 30 ns to the RESET pin. The RESET pin

should be connected to GND (or pulled low) during power-

up of the part. The RESET pin can be pulled high after the

power supplies have settled to nominal values (1.8 V and 3.3

V). At this point, a pulse (pull low and high again) should be

provided to give a RESET to the part.

Most AD6636 pins are driven by both JTAG circuitry and

normal function circuitry specific to each pin. TRST is the

reset pin for JTAG. When TRST is pulled low, JTAG is in

reset and all pins function in normal mode (driven by

functional circuit). If JTAG is not used in the design, the

TRST pin should be pulled low at all times.

相關PDF資料 |

PDF描述 |

|---|---|

| AD6636PCB | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD664(中文) | Monolithic 12-Bit Quad DAC(單片12位四D/A轉換器) |

| AD6640 | 12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640AST | 12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640PCB | 12-Bit, 65 MSPS IF Sampling A/D Converter |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD6636PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636XBCZ | 制造商:Analog Devices 功能描述: |

| AD664 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Monolithic 12-Bit Quad DAC |

| AD6640 | 制造商:AD 制造商全稱:Analog Devices 功能描述:12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640AST | 制造商:Analog Devices 功能描述:ADC Single Pipelined 65Msps 12-bit Parallel 44-Pin LQFP 制造商:Analog Devices 功能描述:ADC SGL PIPELINED 65MSPS 12-BIT PARALLEL 44LQFP - Trays 制造商:Rochester Electronics LLC 功能描述:12-BIT 65 MSPS MONOLITHIC A/D CONVERTER - Tape and Reel 制造商:Analog Devices 功能描述:Analog-Digital Converter IC Number of Bi |

發(fā)布緊急采購,3分鐘左右您將得到回復。