- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366344 > AM188ER-25KCW (ADVANCED MICRO DEVICES INC) CA-BAYONET PDF資料下載

參數(shù)資料

| 型號: | AM188ER-25KCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CA-BAYONET |

| 中文描述: | 16-BIT, 25 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁數(shù): | 44/112頁 |

| 文件大?。?/td> | 2878K |

| 代理商: | AM188ER-25KCW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

44

Am186

TM

ER and Am188

TM

ER Microcontrollers Data Sheet

DRAFT

The integrated peripherals of the Am186ER and

Am188ER microcontrollers are controlled by 16-bit

read/write registers. The peripheral registers are con-

tained within an internal 256-byte control block. The

registers are physically located in the peripheral de-

vices they control, but they are addressed as a single

256-byte block. Figure 9 on page 46 shows a map of

these registers.

Pseudo Static RAM (PSRAM) Support

The Am186ER and Am188ER microcontrollers support

the use of PSRAM devices in low memory chip-select

(LCS) space only. When PSRAM mode is enabled, the

timing for the LCS signal is modified by the chip-select

control unit to provide a CS precharge period during

PSRAM accesses. The 50-MHz timing of the

Am186ER and Am188ER microcontrollers is appropri-

ate to allow 70-ns PSRAM to run with one wait state.

PSRAM mode is enabled through a bit in the Low Mem-

ory Chip-Select (LMCS) Register. The PSRAM feature

is disabled on CPU reset.

In addition to the LCS timing changes for PSRAM pre-

charge, the PSRAM devices also require periodic re-

fresh of all internal row addresses to retain their data.

Although refresh of PSRAM can be accomplished sev-

eral ways, the Am186ER and Am188ER microcontrol-

lers implement auto refresh only.

The Am186ER and Am188ER microcontrollers gener-

ate RFSH, a refresh signal, to the PSRAM devices

when PSRAM mode is enabled. No refresh address is

required by the PSRAM when using the auto refresh

mechanism. The RFSH signal is multiplexed with the

MCS3 signal pin. When PSRAM mode is enabled,

MCS3 is not available for use as a chip-select signal.

The refresh control unit must be programmed before

accessing PSRAM in LCS space. The refresh counter

in the Clock Prescaler (CDRAM) Register must be con-

figured with the required refresh interval value. The re-

fresh counter reload value in the CDRAM Register

should not be set to less than 18 (12h) in order to pro-

vide time for processor cycles between refreshes. The

refresh address counter must be set to 000000h to pre-

vent the MCS

3–MCS0 or PCS6–PCS0 chip selects

from asserting. UCS may randomly assert during a

PSRAM refresh.

LCS is held High and the A bus is not used during re-

fresh cycles. The LMCS Register must be configured to

external ready ignored (R2 = 1) with one wait state

(R1–R0 = 01b), and the PSRAM mode enable bit (SE)

must be set. The ending address of LCS space in the

LMCS Register must also be programmed.

Reading and Writing the PCB

Code intended to execute on the Am188ER microcon-

troller should perform all writes to the PCB registers as

byte writes. These writes will transfer 16 bits of data to

the PCB Register even if an 8-bit register is named in

the instruction. For example,

out dx, al

results in

the

ax

value being written to the port address in

dx

.

Reads to the PCB should be done as word reads. Code

written in this manner will run correctly on the

Am188ER and Am186ER microcontrollers.

Unaligned reads and writes to the PCB result in unpre-

dictable behavior on both the Am186ER and Am188ER

microcontrollers.

For a complete description of all the registers in the

PCB, refer to the

Am186ER and Am188ER Microcon-

trollers User’s Manual

, order #21684.

CLOCK AND POWER MANAGEMENT

The clock and power management unit of the

Am186ER and Am188ER microcontrollers includes a

phase-locked loop (PLL) and a second programmable

system clock output (CLKOUTB).

Phase-Locked Loop (PLL)

In a traditional 80C186/80C188 design, the internal clock

frequency is half the frequency of the crystal. Because of

the internal PLL on the Am186ER and Am188ER micro-

controllers, the internal clock generated by both micro-

controllers can operate at up to four times the frequency

of the crystal. The Am186ER and Am188ER microcon-

trollers operate in the following modes:

n

Divide by Two—Frequency of the system clock is

half the frequency of the crystal with PLL disabled.

n

Times One—Frequency of the system clock will be

the same as the external crystal with PLL enabled.

n

Times Four—Frequency of the system clock is four

times the frequency of the crystal with PLL enabled.

The default Times Four mode must be used for processor

frequencies above 40 MHz. The Divide by Two mode

should be used for frequencies below 16 MHz. The clock-

ing mode is selected using CLKSEL1 and CLKSEL2 on

reset. Table 8 provides the maximum and minimum fre-

quencies for X1, X2, and CLKOUTA according to clocking

mode.

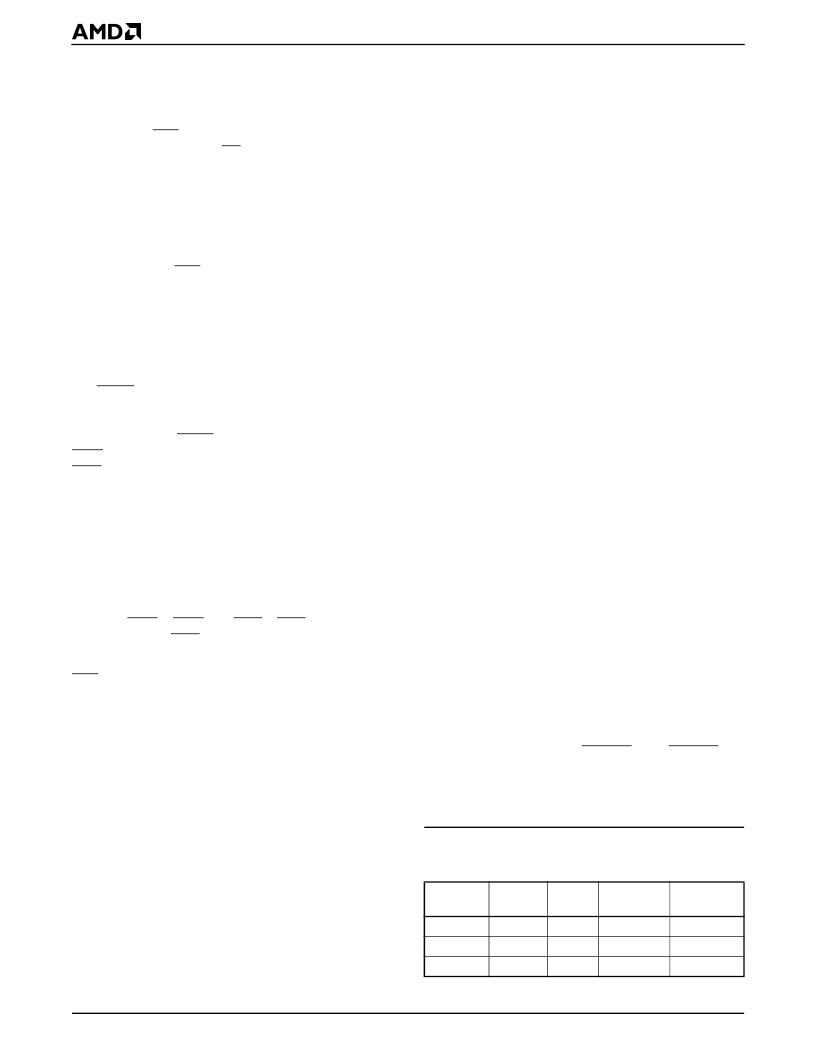

Table 8.

Maximum and Minimum Clock

Frequencies

Mode

Divide by 2

Times 1

Times 4

X1/X2

Max

40 MHz

40 MHz

12.5 MHz

X1/X2

Min

30 MHz

16 MHz

4 MHz

CLKOUTA

Max

20 MHz

40 MHz

50 MHz

CLKOUTA

Min

15 MHz

16 MHz

16 MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM20E-2402SC | 20 watt dc-dc converters |

| AM20E-2403SC | 20 watt dc-dc converters |

| AM20E-2405SC | 20 watt dc-dc converters |

| AM20E-4802SC | 20 watt dc-dc converters |

| AM20E-4803SC | 20 watt dc-dc converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM188ER-25KI/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

| AM188ER-25KIW | 制造商:Advanced Micro Devices 功能描述:MCU 16-bit E86 CISC ROMLess 3.3V 100-Pin PQFP 制造商:AMD (Advanced Micro Devices) 功能描述:MCU 16-bit E86 CISC ROMLess 3.3V 100-Pin PQFP |

| AM188ER-25VC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

| AM188ER-25VCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:High-Performance, 80C186- and 80C188-Compatible, 16-Bit Embedded Microcontrollers with RAM |

| AM188ER-25VD\\W | 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。