- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366344 > AM188ER-25KCW (ADVANCED MICRO DEVICES INC) CA-BAYONET PDF資料下載

參數(shù)資料

| 型號: | AM188ER-25KCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CA-BAYONET |

| 中文描述: | 16-BIT, 25 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁數(shù): | 48/112頁 |

| 文件大?。?/td> | 2878K |

| 代理商: | AM188ER-25KCW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

48

Am186

TM

ER and Am188

TM

ER Microcontrollers Data Sheet

DRAFT

Note:

Power-save operation requires that clock-

dependent peripherals be reprogrammed for clock

frequency changes. Software drivers must be aware of

clock frequency.

Initialization and Processor Reset

Processor initialization or startup is accomplished by

driving the RES input pin Low. RES must be held Low

for 1 ms during power-up to ensure proper device ini-

tialization. RES forces the Am186ER and Am188ER

microcontrollers to terminate all execution and local

bus activity. No instruction or bus activity occurs as long

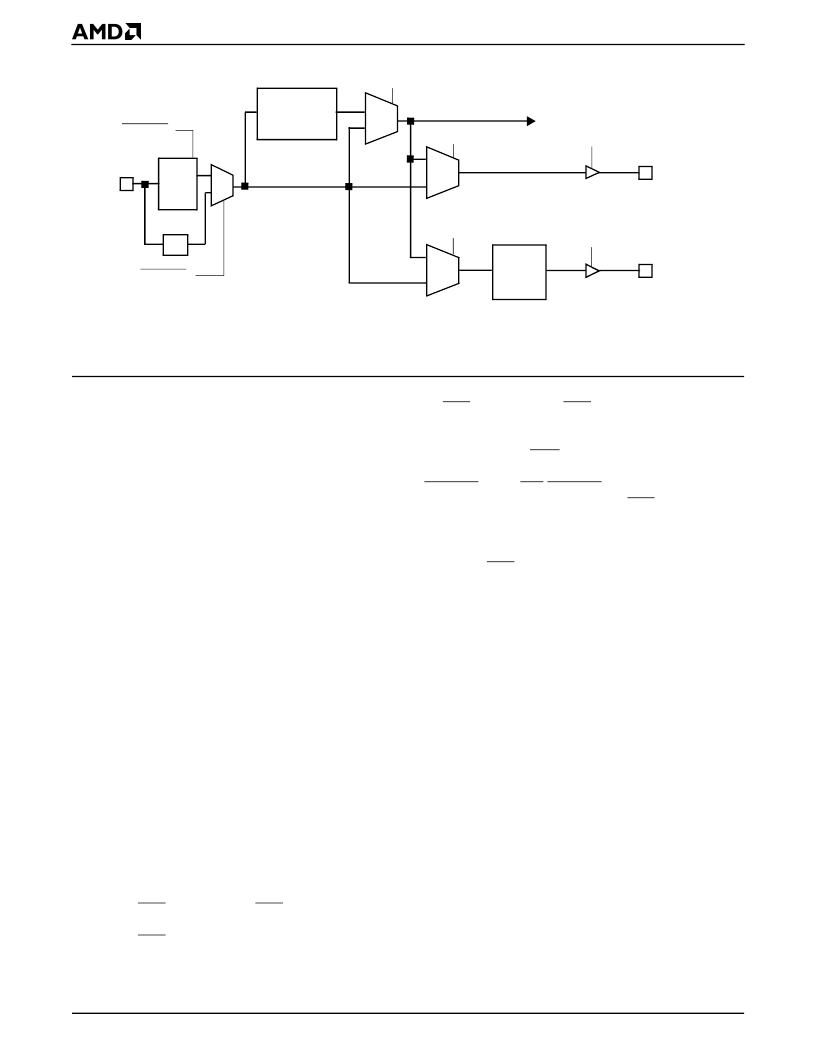

Figure 10. Clock Organization

System Clocks

The base system clock of the original Am186/Am188

microcontrollers is renamed CLKOUTA and the addi-

tional output is called CLKOUTB. CLKOUTA and CLK-

OUTB operate at either the fundamental processor

frequency or the CPU clock (power-save) frequency.

Figure 10 shows the organization of the clocks.

The second clock output (CLKOUTB) allows one clock

to run at the fundamental frequency and the other clock

to run at the CPU (power-save) frequency. Individual

drive enable bits allow selective enabling of just one, or

both, of these clock outputs.

Power-Save Operation

The Power-Save mode of the Am186ER and

Am188ER microcontrollers reduces power consump-

tion and heat dissipation, thereby extending battery life

in portable systems. In Power-Save mode, operation of

the CPU and internal peripherals continues at a slower

clock frequency. When a hardware interrupt occurs, the

microcontroller automatically returns to its normal op-

erating frequency. The microcontroller remains in

Power-Save mode for software interrupts and traps.

as RES is active. After RES becomes inactive and an

internal processing interval elapses, the microcontrol-

ler begins execution with the instruction at physical lo-

cation FFFF0h. RES also sets some registers to

predefined values. Note that all clock selection (S6/

CLKSEL1 and UZI/CLKSEL2) must be stable four

clocks prior to the deassertion of RES. Activating the

PLL will require 1 ms to achieve a stable clock.

Reset Configuration Register

When the RES input is asserted Low, the contents of

the address/data bus (AD15–AD0) are written into the

Reset Configuration Register. The system can place

configuration information on the address/data bus

using weak external pullup or pulldown resistors, or

using an external driver that is enabled during reset.

The processor does not drive the address/data bus

during reset.

For example, the Reset Configuration Register could

be used to provide the software with the position of a

configuration switch in the system. Using weak external

pullup and pulldown resistors on the address and data

bus, the system would provide the microcontroller with

a value corresponding to the position of the jumper dur-

ing a reset.

The Reset Configuration Register can only be modified

during reset. This register is read-only during normal

operation.

Power-Save

Divisor

1

(/1 to /128)

CBF

1

Mux

CAF

1

Mux

PSEN

1

PLL

1x or 4x

Mux

CLKOUTA

CLKOUTB

X1, X2

CPU Clock

Time

Delay

6

±

2.5ns

÷

2

Input Clock

CLKSEL2

CLKSEL1

CAD

1

CBD

1

Fundamental

Clock

Mux

Notes:

1. Set via PDCON Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM20E-2402SC | 20 watt dc-dc converters |

| AM20E-2403SC | 20 watt dc-dc converters |

| AM20E-2405SC | 20 watt dc-dc converters |

| AM20E-4802SC | 20 watt dc-dc converters |

| AM20E-4803SC | 20 watt dc-dc converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM188ER-25KI/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

| AM188ER-25KIW | 制造商:Advanced Micro Devices 功能描述:MCU 16-bit E86 CISC ROMLess 3.3V 100-Pin PQFP 制造商:AMD (Advanced Micro Devices) 功能描述:MCU 16-bit E86 CISC ROMLess 3.3V 100-Pin PQFP |

| AM188ER-25VC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

| AM188ER-25VCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:High-Performance, 80C186- and 80C188-Compatible, 16-Bit Embedded Microcontrollers with RAM |

| AM188ER-25VD\\W | 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。