- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376804 > DM9801A PDF資料下載

參數(shù)資料

| 型號(hào): | DM9801A |

| 文件頁數(shù): | 30/60頁 |

| 文件大小: | 605K |

| 代理商: | DM9801A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

DM9801A

1M Home Phoneline Network Physical Layer Single Chip Transceiver

17.6

RX_PWR

0, RO

Receive Power:

This bit is an indication of the current receive signal power.

1= The receive signal power is high.

0= The receive signal power is low.

17.5

RX_SPD

0, RO

Receive Speed:

This bit is an indication of the current receive speed.

1= The receive speed is high.

0= The receive speed is low.

17.4

RX_VER

0, RO

Receive Version:

This bit is an indication of the current receive version.

1= The receive version is not version 0.

0= The receive version is version 0.

17.3 -

17.0

Write as 0, ignore on read

30

Final

Version: DM9801A-DS-F01

May 30, 2001

Reserved

<0101>, RW

Reserved:

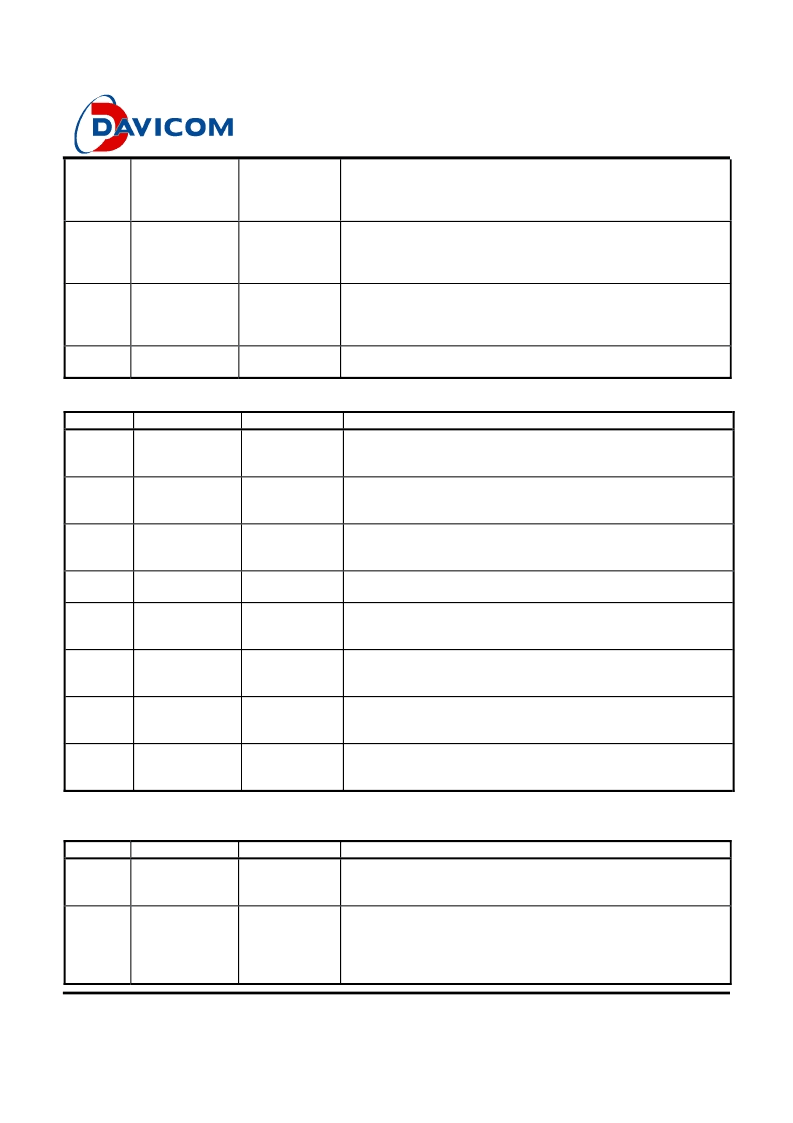

IMASK (Interrupt Mask) Register - Register 18

Bit

Bit Name

18.15 –

18.10

Interrupts

Default

0,RW

Description

Software

Software Interrupts:

1= Software interrupts will not activate the INT# pin

0= Software interrupts will activate the INT# pin

Mask RXPCOM Valid:

1= RX_PCOM_VAL will not activate the INT# pin

0= RX_PCOM_VAL will activate the INT# pin

Mask TXPCOM Ready:

1= TX_PCOM_RDY will not activate the INT# pin

0= TX_PCOM_RDY will activate the INT# pin

Reserved:

Write as 0, ignore on read

Mask Packet Received:

1= Packet Received will not activate the INT# pin

0= Packet Received will activate the INT# pin

Packet Transmitted:

1= Packet Transmitted will not activate the INT# pin

0= Packet Transmitted will activate the INT# pin

Remote Command Received:

1= Remote Command Received will not activate the INT# pin

0= Remote Command Received will activate the INT# pin

Remote Command Sent:

1= Remote Command Sent will not activate the INT# pin

0= Remote Command Sent will activate the INT# pin.

18.9

MSK_RX_PCOM

0,RW

18.8

MSK_TX_PCOM

0,RW

18.7 –

18.4

18.3

Reserved

0,RW

MSK_PKT_RCV

0,RW

18.2

MSK_PKT_XMIT

0,RW

18.1

MSK_RMT_RCV

0,RW

18.0

MSK_CMD_SNT

0,RW

ISTAT (Interrupt Status) Register - Register 19

This register reports the state of each interrupt source regardless of the state of the IMASK Register.

Bit

Bit Name

Default

19.15 –

19.10

Interrupts

Description

Software

0,RW

Software Interrupts:

When set any bit of those registers indicates software interrupt

is on.

RXPCOM Valid:

When set this bit indicates a non-null RX_PCOM has been

received.

Accessing the high byte of the RX_PCOM register clears this

bit.

19.9

RX_PCOM_VAL

0,RW

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9801E | 1M home Phonrline Network Physical Layer Single Chip Transceiver |

| DMA2271 | Consumer IC |

| DMA2280 | Consumer IC |

| DMA2281 | Consumer IC |

| DMA2275 | DMA 2275, DMA 2286 C/D/D2-MAC Descrambler |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9801AE | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:1M Home Phoneline Network Physical Layer Single Chip Transceiver |

| DM9801E | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1M home Phonrline Network Physical Layer Single Chip Transceiver |

| DM9B | 功能描述:數(shù)字萬用表 4000 COUNT AUTO RoHS:否 制造商:Tektronix 產(chǎn)品:Multimeters 類型:Bench 準(zhǔn)確性:0.04 % 電壓范圍:2 V to 2 kV 電阻范圍: 電容范圍: 顯示計(jì)數(shù): 頻率:10 Hz to 45 Hz, 850 Hz to 1 MHz 測(cè)距: 真均方根值: 數(shù)據(jù)保持: |

| D-M9B | 制造商:SMC Corporation of America 功能描述:Sensor, solid state, direct mount, grommet connection, for MX/MH/CQ2/NCQ2/NCQ8 制造商:SMC 功能描述:2-Wire Auto Switch for 24Vdc Relay/PLC |

| D-M9BA | 制造商:SMC Corporation of America 功能描述:Autoswitch, water resistant, 2 wire, horizontal |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。