- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359352 > VCT3801A (MICRONAS SEMICONDUCTOR HOLDING AG) Video/Controller/Teletext IC Family PDF資料下載

參數(shù)資料

| 型號(hào): | VCT3801A |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Video/Controller/Teletext IC Family |

| 中文描述: | 視頻/控制/圖文電視IC系列 |

| 文件頁數(shù): | 38/172頁 |

| 文件大小: | 2243K |

| 代理商: | VCT3801A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁

VCT 38xxA

ADVANCE INFORMATION

38

Micronas

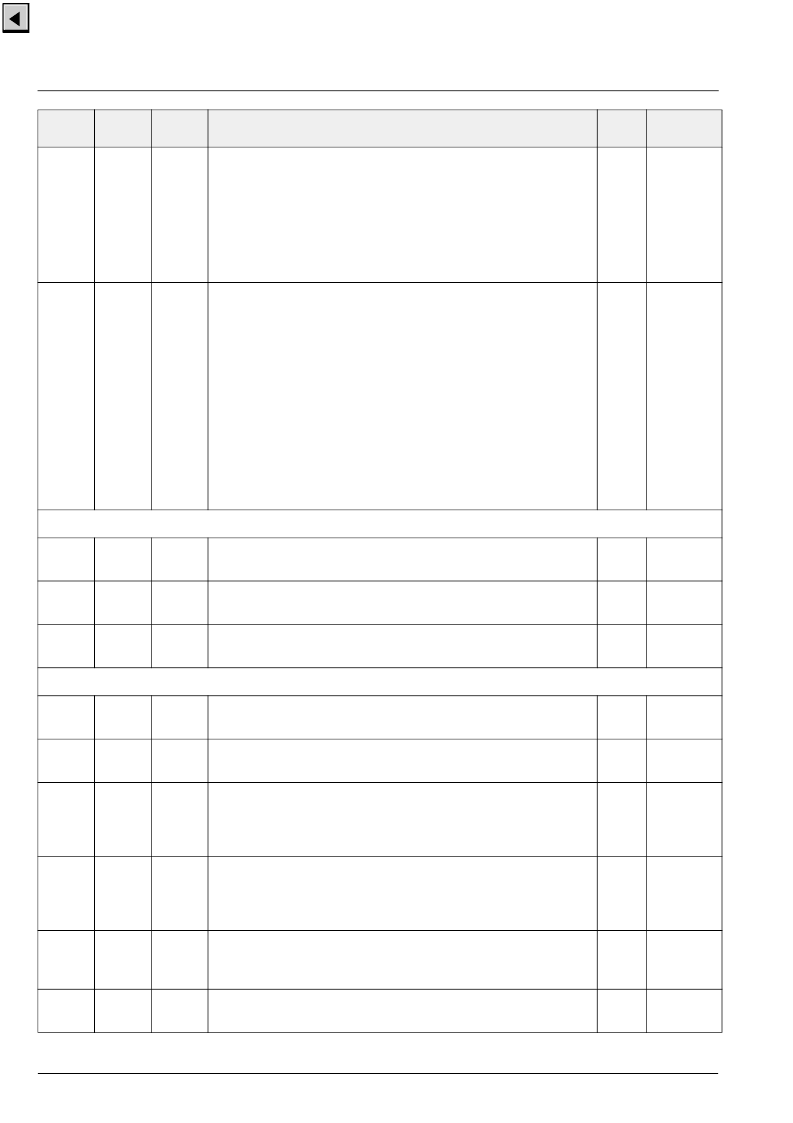

h’18

h’19

h’1a

h’1d

h’1c

h’1b

8

r

measurement result registers

minimum in active picture

maximum in active picture

white drive

cutoff/leakage red

cutoff/leakage green

cutoff/leakage blue,

read pulse starts tube measurement

MRMIN

MRMAX

MRWDR

MRCR

MRCG

MRCB

h’1e

8

r

measurement adc status and Fast-Blank input status

measurement status register

bit [0]

0/1

bit [2:1]

00

01

10

11

bit [3]

0/1

0/1

bit [5]

1

tube measurement active / complete

white drive measurement cycle

red

green

blue

reserved

picture measurement active / complete

Fast-Blank input Low / High (static)

Fast-Blank input negative transition since

last read (bit reset at read)

reserved

bit [7:6]

PMS

Vertical Timing

h’67

9

w v

vertical blanking start

bit [8:0]

0..511

first line of vertical blanking

305

VBST

h’77

9

w v

vertical blanking stop

bit [8:0]

0..511

last line of vertical blanking

25

VBSO

h’5f

9

w v

vertical free run period

bit [8:0] free running field period = (value+4) lines

309

VPER

Horizontal Deflection and Timing

h’7a

9

w v

quadratic term of angle & bow correction

bit [8:0]

256..+255

(

±

500 ns)

0

BOW

h’76

9

w v

linear term of angle & bow correction

bit [8:0]

256..+255

(

±

500 ns)

0

ANGLE

h’6e

9

w v

adjustable delay of PLL2, clamping, and blanking (relative to

front sync)

adjust clamping pulse for analog RGB input

bit [8:0]

256..+255

(

±

8

μ

s)

141

POFS2

h’72

9

w v

adjustable delay of flyback, main sync, csync and analog RGB

(relative to PLL2)

adjust horizontal drive or csync

bit [8:0]

256..+255

(

±

8

μ

s)

0

POFS3

h’7e

9

w v

adjustable delay of main sync (relative to flyback)

adjust horizontal position for digital picture

bit [8:0]

20 steps

=

1

μ

s

120

HPOS

h’5b

9

w v

start of horizontal blanking

bit [8:0]

0..511

1

HBST

I

2

C Sub

address

Number

of bits

Mode

Function

Default

Name

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VCU2133 | High-Speed coder/decoder IC |

| VCX2150A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCX2154A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCXO-105N | VCXO |

| VCXO-199 | VCXO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VCT3802A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3803A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3804A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3811A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3831A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。