- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359352 > VCT3801A (MICRONAS SEMICONDUCTOR HOLDING AG) Video/Controller/Teletext IC Family PDF資料下載

參數(shù)資料

| 型號: | VCT3801A |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Video/Controller/Teletext IC Family |

| 中文描述: | 視頻/控制/圖文電視IC系列 |

| 文件頁數(shù): | 94/172頁 |

| 文件大小: | 2243K |

| 代理商: | VCT3801A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁當前第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁

VCT 38xxA

ADVANCE INFORMATION

94

Micronas

5.7.4. External Reset Sources

As long as the reset input comparator on the pin

RESQ detects the Low level, the VCT 38xxA is in reset

state. On this pin, external reset sources may be wire-

ored with the internal reset sources, leading to a sys-

tem-wide reset signal combining all system reset

sources.

5.7.5. Summary of Module Reset States

After reset, the controller modules are set to the follow-

ing reset states:

5.7.6. Reset Registers

This register controls the reset logic and clock genera-

tion.

ALI

r1:

r0:

w1:

Alarm Interrupt

Alarm was interrupt source

no pending alarm interrupt

reset alarm interrupt

VSI

r1:

r0:

w1:

VSUP

D

Voltage Supervision Interrupt

VSUP

D

supervision was interrupt source

no pending VSUP

D

supervision interrupt

reset VSUP

D

supervision interrupt

TPUI

r1:

r0:

w1:

TPU Watchdog Interrupt

TPU watchdog was interrupt source

no pending TPU watchdog interrupt

reset TPU interrupt flag

If the source of one of these interrupts is still active,

resetting the interrupt flag will not work and no further

interrupt will be generated.

I2CEN

r/w1:

r/w0:

I2C Enable

Enable I2C output from FE/BE.

Disable I2C output.

DCOCLP

r/w1:

r/w0:

DCO clamping

DCO input clamped to 0.

DCO input controlled by front-end.

SELCLK

r/w1:

r/w0:

Select clock source

From PLL.

From DCO.

RESDIS

r/w1:

r/w0:

Reset Disable

Disable internal CPU reset.

Enable internal CPU reset.

RESOUT

w1:

w0:

RESQ Output

RESQ output active.

RESQ output inactive.

This register controls the Supply and Clock Supervi-

sion modules.

CSA

w1:

w0:

Clock and Supply Supervision Active

Both Enabled.

Both Disabled.

This register controls the Watchdog module. Only val-

ues between 1 and 255 are allowed.

WDRES

r1:

w:

Watchdog Reset Source

Watchdog was reset source.

Any write access to CSW1 resets this

flag.

First write the desired watchdog time value to this reg-

ister. On further writes, to retrigger the Watchdog,

alternatingly write a value (not necessarily the former

time value) and its bit complemented value. Never

change the latter value.

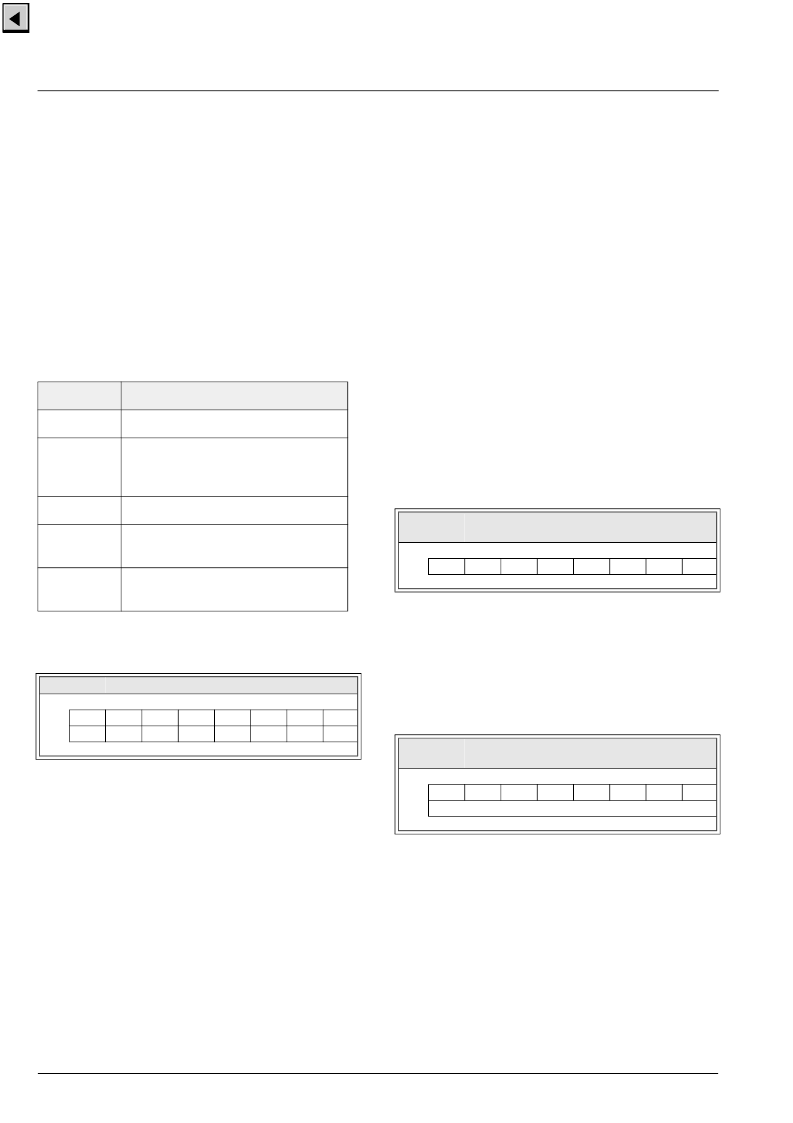

Table 5–6:

Status after reset

Module

Status

CPU

CPU Fast mode.

Interrupt

Controller

Interrupts are disabled. Priority reg-

isters, request flip-flops and stack

are cleared.

Ports

Normal mode. Output is tristate.

Watchdog

Switched off. SW activation is pos-

sible.

Clock

monitor

EMU IC: Active. SW may toggle.

normal IC: Permanently active.

28:

1F07

29:

RC

30:

Reset Control Register

bit

7

6

5

4

3

2

1

0

w

ALI

VSI

TPUI

I2CEN

DCOCLP SELCLK RESDIS RESOUT

r

ALI

VSI

TPUI

I2CEN

DCOCLP SELCLK RESDIS

0

reset

0

0

0

0

1

0

0

0

31:

1F00

32:

CSW0

33:

Clock, Supply & Watchdog Regis-

ter 0

bit

7

6

5

4

3

2

1

0

w

x

x

x

x

x

x

x

CSA

reset

x

x

x

x

x

x

x

1

34:

1F60

35:

CSW1

36:

Clock, Supply & Watchdog Regis-

ter 1

bit

7

6

5

4

3

2

1

0

r

x

x

x

x

x

x

x

WDRES

w

Watchdog Time and Trigger Value

reset

1

1

1

1

1

1

1

1

相關PDF資料 |

PDF描述 |

|---|---|

| VCU2133 | High-Speed coder/decoder IC |

| VCX2150A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCX2154A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCXO-105N | VCXO |

| VCXO-199 | VCXO |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| VCT3802A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3803A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3804A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3811A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3831A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

發(fā)布緊急采購,3分鐘左右您將得到回復。