- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359352 > VCT3801A (MICRONAS SEMICONDUCTOR HOLDING AG) Video/Controller/Teletext IC Family PDF資料下載

參數(shù)資料

| 型號: | VCT3801A |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Video/Controller/Teletext IC Family |

| 中文描述: | 視頻/控制/圖文電視IC系列 |

| 文件頁數(shù): | 47/172頁 |

| 文件大?。?/td> | 2243K |

| 代理商: | VCT3801A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當前第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁

ADVANCE INFORMATION

VCT 38xxA

Micronas

47

3. Text and OSD Processing

3.1. Introduction

The VCT 38xxA includes a World System Teletext

(WST) decoder, whose display capabilities are also

used for OSD generation. In the following sections the

text and OSD processing part of the VCT 38xxA will be

named TPU for short.

With integrated CPU, RAM and ROM, an adaptive data

slicer, a display controller, and a number of interfaces,

the TPU offers acquisition and display of various tele-

text and data services such as WST, PDC, VPS, and

WSS. Fig. 3–1 shows the functional block diagram of

the TPU.

The TPU operates independently from the TV control-

ler and can be controlled by software via I

2

C bus inter-

face (see Section 3.14. on page 82). The TV controller

is not burdened with the task of teletext decoding and

communicates with the TPU via a high-level command

language.

The TPU performs the following tasks:

– teletext data acquisition

(hardware)

– teletext data decoding

(software)

– page generation

(software)

– page memory management

(software)

– page display

(hardware)

– user interface

(software)

3.2. SRAM Interface

The SRAM interface connects a standard SRAM to the

internal bus structure. The address bus is 19 bit wide,

addressing SRAMs up to 4 Mbit. Smaller SRAMs can

also be connected.

The SRAM interface has to handle 3 asynchronous

data streams. The CPU needs access to every mem-

ory location of the SRAM. During VBI the slicer writes

up to 22 teletext lines of 43 Bytes into the acquisition

scratch memory. During text display the display con-

troller copies teletext rows from display memory into its

internal row buffer.

On VCT 38xxA the SRAM interface of the TPU is con-

nected to the memory bus of the TV controller. This is

done to save pins and to give the TV controller faster

access to the display memory. Refer to DMA Interface

(chapter 5.9. on page 96) for more details.

After reset the TPU will not use the SRAM interface

until receiving the I

2

C command “DRAM_MODE” (see

Section 3.12. on page 68).

3.3. Text Controller

The TPU operates with its own 65C02 core running at

10.125 MHz. The core can address up to 64 kBytes of

memory.

The CPU memory contains 640 Bytes RAM, 12 kBytes

program ROM and 12 kBytes character ROM. The

character ROM holds the font data and is separated

from the program ROM to save CPU time. The CPU

can still access the character ROM via a DMA inter-

face including wait cycles. The display controller can

also access the CPU memory via the same DMA inter-

face. By this means it is possible to locate part of the

character font in program ROM or part of the program

code in character ROM.

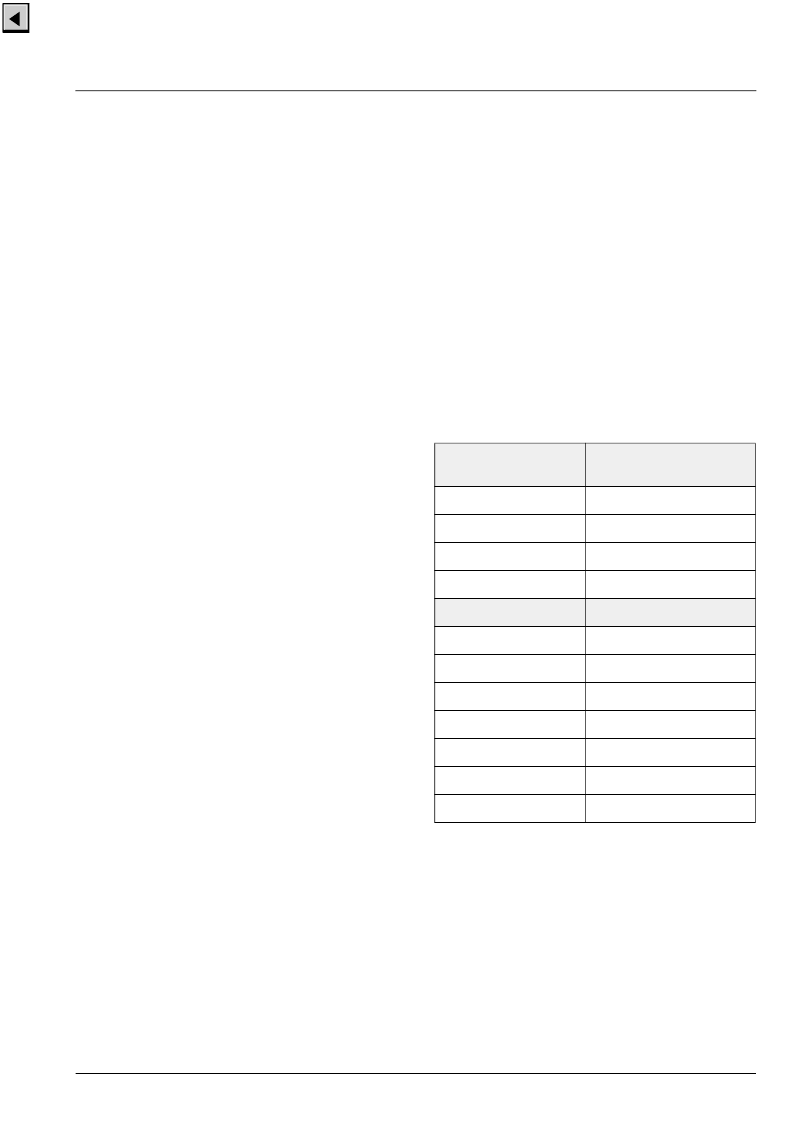

Table 3–1:

Memory map of text controller

Interrupt Vector

Absolute Address

(High Byte, Low Byte)

IRQ

FFFF, FFFE

Reset

FFFD, FFFC

NMI

FFFB, FFFA

Control Word

FFF9

Memory Segment

Absolute Address

Zero Page

0000

00FF

Stack Page

0100

01FF

OSD Buffer

0100

019F

I/O Page

0200

02FF

Extra Page

0300

037F

Character ROM

5000

7FFF

Program ROM

D000

FFFF

相關PDF資料 |

PDF描述 |

|---|---|

| VCU2133 | High-Speed coder/decoder IC |

| VCX2150A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCX2154A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCXO-105N | VCXO |

| VCXO-199 | VCXO |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| VCT3802A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3803A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3804A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3811A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3831A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

發(fā)布緊急采購,3分鐘左右您將得到回復。