- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359352 > VCT3801A (MICRONAS SEMICONDUCTOR HOLDING AG) Video/Controller/Teletext IC Family PDF資料下載

參數(shù)資料

| 型號: | VCT3801A |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Video/Controller/Teletext IC Family |

| 中文描述: | 視頻/控制/圖文電視IC系列 |

| 文件頁數(shù): | 49/172頁 |

| 文件大小: | 2243K |

| 代理商: | VCT3801A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁

ADVANCE INFORMATION

VCT 38xxA

Micronas

49

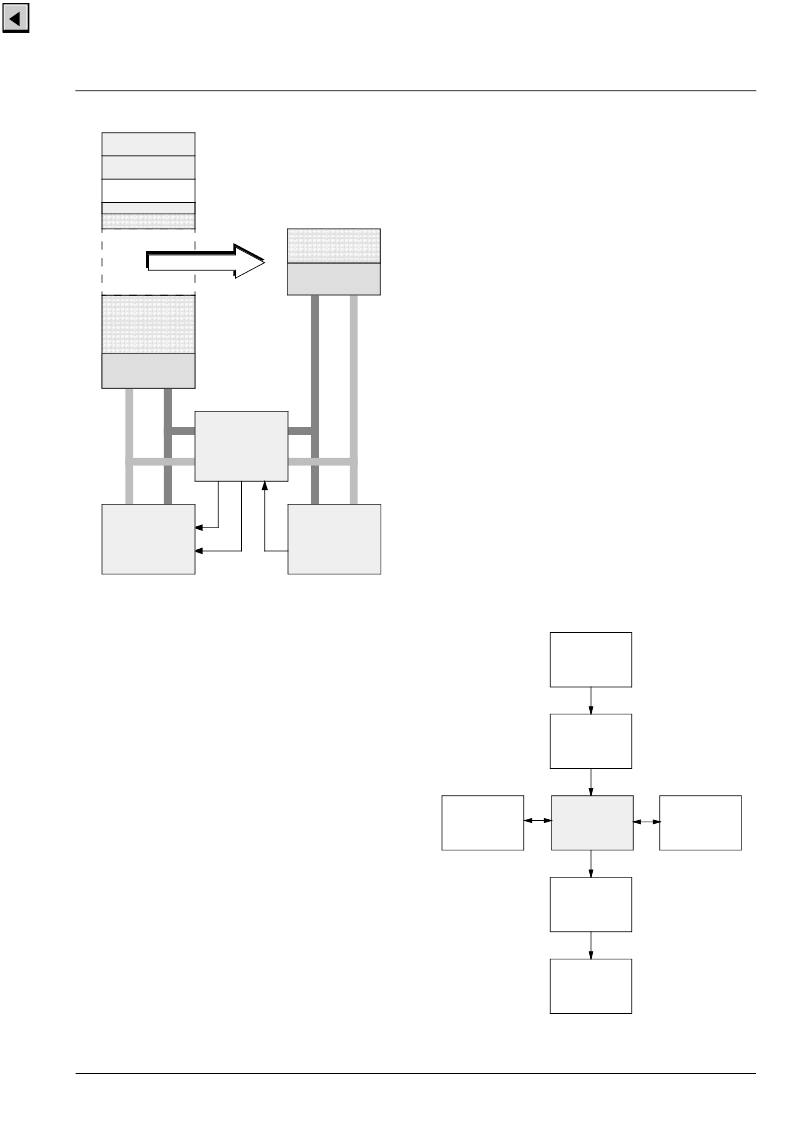

Fig. 3–2:

Memory environment of text controller

3.4. Teletext Acquisition

The only task of the slicer circuit is to extract teletext

lines from the incoming composite video signal and to

store them into the acquisition scratch buffer of the

internal/external SRAM. No page selection is done at

this hardware level.

Four analog sources can be connected, thus it is pos-

sible to receive text from one channel while watching

another on the screen. After clamping and AGC ampli-

fier the analog video signal is converted into binary

data. Sync separation is done by a sync slicer and a

horizontal PLL, which generate the horizontal and ver-

tical timing. By these means, no external sync signals

are needed and any available signal source can be

used for teletext reception.

The teletext information itself is acquired using adap-

tive slicers on bit and byte level with soft error detec-

tion to decrease the bit error rate under bad reception

conditions. The slicer can be programmed to different

bit rates for reception of PAL, NTSC or MAC world sys-

tem teletext as well as VPS, WSS, or CAPTION sig-

nals.

3.5. Teletext Page Management

As a state-of-the-art teletext decoder, the TPU is able

to store and manage a sufficient number of teletext

pages to absorb the annoying transmission cycle

times. The number of available pages is only limited by

the memory size. With an intelligent software and a

4-Mbit SRAM it is possible to store and to control more

than 500 teletext pages.

The management of such a data base is a typical soft-

ware task and is therefore performed by the 65C02.

Using a fixed length page table with one entry for every

possible page, the software distributes the content of

the acquisition scratch buffer among the page memory.

The page size is fixed to 1 kByte, only ghost rows are

chained in 128-Byte segments to avoid unused mem-

ory space.

A stored teletext page cannot be displayed directly,

because of the row-adaptive transmission and the

level 2 enhancements (row 26

29). Therefore, the

CPU has to transfer the selected teletext page into a

display page buffer, adding extra data such as charac-

ter set extension and non-spacing attributes.

3.5.1. Memory Manager

The Memory manager is the core of the internal TPU

firmware. Most of the acquisition and display related

functions are controlled by this management.

Fig. 3–3:

Memory Manager

DMA

Interface

12K

Program ROM

12K

Character ROM

Zero Page

Stack Page

I/O Page

ADR

DATA

BE

RDY

65C02

BUSREQ

Display

DATA

ADR

Extra Page

8000

1000

0000

D000

Display

Memory

Memory

Manager

Display

Controller

Page

Memory

Page

Table

Scratch

Memory

Acquisition

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VCU2133 | High-Speed coder/decoder IC |

| VCX2150A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCX2154A | Surface mount 15.88 mm SQ (.625 SQ) |

| VCXO-105N | VCXO |

| VCXO-199 | VCXO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VCT3802A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3803A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3804A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3811A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

| VCT3831A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video/Controller/Teletext IC Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。