- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4592 > AD5522JSVDZ (Analog Devices Inc)IC PMU QUAD 16BIT DAC 80-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | AD5522JSVDZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 41/64頁 |

| 文件大小: | 0K |

| 描述: | IC PMU QUAD 16BIT DAC 80-TQFP |

| 產(chǎn)品變化通告: | Improve FI ac crosstalk |

| 設(shè)計(jì)資源: | Parametric Measurement Unit and Supporting Components for PAD Appls Using AD5522 and AD7685 (CN0104) |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 類型: | 每引腳參數(shù)測(cè)量單元(PPMU) |

| 應(yīng)用: | 自動(dòng)測(cè)試設(shè)備 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 80-TQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 80-TQFP(12x12) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 798 (CN2011-ZH PDF) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

AD5522

Data Sheet

Rev. E | Page 46 of 64

WRITE SYSTEM CONTROL REGISTER

The system control register is accessed when the PMU channel

address bits (PMU3 to PMU0) and the mode bits (MODE1 and

MODE0) are all 0s. This register allows quick setup of various

functions in the device. The system control register operates on

a per-device basis.

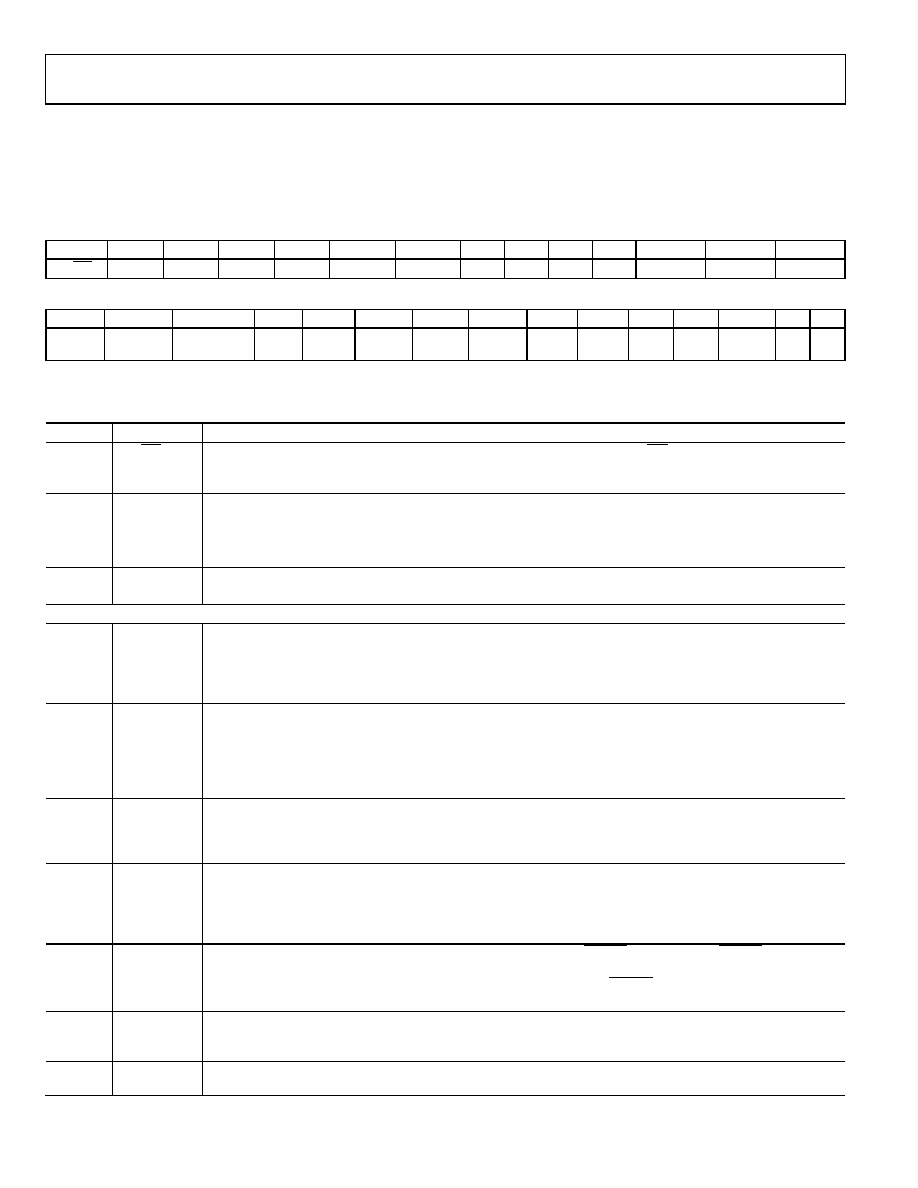

Table 21. System Control Register Bits—Bit B28 to Bit B15

B28

B27

B26

B25

B24

B23

B22

B21

B20

B19

B18

B17

B16

B15

RD/WR

PMU3

PMU2

PMU1

PMU0

MODE1

MODE0

CL3

CL2

CL1

CL0

CPOLH3

CPOLH2

CPOLH1

Table 22. System Control Register Bits—Bit B14 to Bit B0

B14

B13

B12

B11

B10

B9

B8

B7

B6

B5

B4

B3

B2

B11

B01

CPOLH0

CPBIASEN

DUTGND/CH

Guard

ALM

Clamp

ALM

INT10K

Guard

EN

GAIN1

GAIN0

TMP

enable

TMP1

TMP0

Latched

0

1

Bit B1 and Bit B0 are unused data bits.

Table 23. System Control Register Functions

Bit

Bit Name

Description

28 (MSB)

RD/WR

When low, a write function takes place to the selected register; setting the RD/WR bit high initiates a readback

sequence of the PMU, alarm status, comparator status, system control, or DAC register, as determined by the

address bits.

27

PMU3

Set Bit PMU3 to Bit PMU0 to 0 to address the system control register.

26

PMU2

25

PMU1

24

PMU0

23

MODE1

Set the MODE1 and MODE0 bits to 0 to address the system control register.

22

MODE0

System Control Register-Specific Bits

21

CL3

Current or voltage clamp enable. Bit CL3 to Bit CL0 enable and disable the current or voltage clamp function per

channel (0 = disable; 1 = enable). The clamp enable function is also available in the PMU register on a per-

channel basis. This dual functionality allows flexible enabling or disabling of this function. When reading back

information about the status of the clamp enable function, the data that was most recently written to the clamp

register is available in the readback word from either the PMU register or the system control register.

20

CL2

19

CL1

18

CL0

17

CPOLH3

Comparator output enable. By default, the comparator outputs are high-Z on power-on. A 1 in each bit position

enables the comparator output for the selected channel. Bit 13 (CPBIASEN) must be enabled to power on the

comparator functions. The comparator enable function is also available in the PMU register on a per-channel

basis. This dual functionality allows flexible enabling or disabling of this function. When reading back information

about the status of the comparator enable function, the data that was most recently written to the comparator

status register is available in the readback word from either the PMU register or the system control register.

16

CPOLH2

15

CPOLH1

14

CPOLH0

13

CPBIASEN

Comparator enable. By default, the comparators are powered down when the device is powered on. To enable

the comparator function for all channels, write a 1 to this bit. A 0 disables the comparators and shuts them

down. The comparator output enable bits (CPOLHx, Bit 17 to Bit 14) allow the user to turn on each comparator

output individually, enabling busing of comparator outputs.

12

DUTGND/CH

DUTGND per channel enable. The GUARDINx/DUTGNDx pins are shared pins that can be configured to enable a

DUTGND per PMU channel or a guard input per PMU channel. Setting this bit to 1 enables DUTGND per

channel. In this mode, the pin functions as a DUTGND pin on a per-channel basis. The guard inputs are

disconnected from this pin and instead are connected directly to the MEASVHx line by an internal connection.

The default power-on condition is GUARDINx.

11

GUARD ALM

Clamp and guard alarm functions share one open-drain alarm pin (CGALM). By default, the CGALM pin is

disabled. The guard ALM and clamp ALM bits allow the user to choose whether clamp alarm information, guard

alarm information, or both sets of alarm information are flagged by the CGALM pin. Set high to enable either

alarm function.

10

CLAMP ALM

9

INT10K

Internal sense short. Setting this bit high allows the user to connect an internal sense short resistor of 10 kΩ

(4 kΩ + 2 kΩ switch + 4 kΩ) between the FOHx and the MEASVHx lines (SW7 is closed). Setting this bit high also

closes SW15, allowing the user to connect another 10 kΩ resistor between DUTGNDx and AGND.

8

Guard EN

Guard enable. The guard amplifier is disabled on power-on; to enable the guard amplifier, set this bit to 1. If the

guard function is not in use, disabling it saves power (typically 400 μA per channel).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ESC65DRTI | CONN EDGECARD 130PS DIP .100 SLD |

| AMC30DRTS | CONN EDGECARD 60POS .100 DIP SLD |

| AMC30DRES | CONN EDGECARD 60POS .100 EYELET |

| ASC31DRAS | CONN EDGECARD 62POS .100 R/A DIP |

| RGM40DTMT | CONN EDGECARD 80POS R/A .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD5522JSVUZ | 功能描述:IC PMU QUAD 16BIT DAC 80-TQFP RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| AD5522JSVUZ-RL | 功能描述:Per-Pin Parametric Measurement Unit (PPMU) IC Automatic Test Equipment 80-TQFP-EP (12x12) 制造商:analog devices inc. 系列:- 包裝:帶卷(TR) 零件狀態(tài):有效 類型:每引腳參數(shù)測(cè)量單元(PPMU) 應(yīng)用:自動(dòng)測(cè)試設(shè)備 安裝類型:表面貼裝 封裝/外殼:80-TQFP 裸露焊盤 供應(yīng)商器件封裝:80-TQFP-EP(12x12) 標(biāo)準(zhǔn)包裝:1,000 |

| AD5523JCPZ | 制造商:AD 制造商全稱:Analog Devices 功能描述:Quad Parametric Measurement Unit With Integrated 16-Bit Level Setting DACs |

| AD5530 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Serial Input, Voltage Output 12-/14-Bit DACs |

| AD5530_07 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Serial Input, Voltage Output 12-/14-Bit Digital-to-Analog Converters |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。