- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375989 > FW82801E (Intel Corp.) Intel 82801E Communications I/O Controller Hub (C-ICH) PDF資料下載

參數(shù)資料

| 型號: | FW82801E |

| 廠商: | Intel Corp. |

| 英文描述: | Intel 82801E Communications I/O Controller Hub (C-ICH) |

| 中文描述: | 英特爾82801E通訊I / O控制器集線器(丙,出血) |

| 文件頁數(shù): | 46/84頁 |

| 文件大小: | 1196K |

| 代理商: | FW82801E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

Intel

82801E C-ICH

46

Advance Information Datasheet

3.2.17

SIU LPC Interface

SIU0_RI#

SIU1_RI#

I

Ring Indicator for UART0 and UART1:

Active low, this pin indicates that a

telephone ringing signal has been received by the external agent.

NOTE:

These pins are Modem Status Input whose condition can be tested by

the processor by reading bit 6 (RI) of the Modem Status register (MSR).

Bit 6 is the complement of the RI# signal. Bit 2 (TERI) of the MSR

indicates whether the DCD# input has changed state since the previous

reading of the MSR. When the RI bit of the MSR changes state an

interrupt is generated if the Modem Status Interrupt is enabled.

SIU0_RTS#

SIU1_RTS#

O

Request to Send for UART0 and UART1:

When low these pins informs the

modem or data set that 82801E C-ICH UART0 and UART1 are ready to establish

a communication link. The RTS#x(x=0,1) output signals can be set to an active

low by programming the RTSx (x-0,1) (bit1) of the Modem control register to a

logic ‘1’. A Reset operation sets this signal to its inactive state (logic ‘1’). LOOP

mode operation holds this signal in its inactive state.

SIU0_RXD

SIU1_RXD

I

Serial Inputs for UART0 and UART1:

Serial data input from device pin to the

receive port.

SIU0_TXD

SIU1_TXD

O

Serial Output for UART0 and UART1:

Serial data output to the communication

peripheral/modem or data set. Upon reset, the TXD pins will be set to MARKING

condition (logic ‘1’ state).

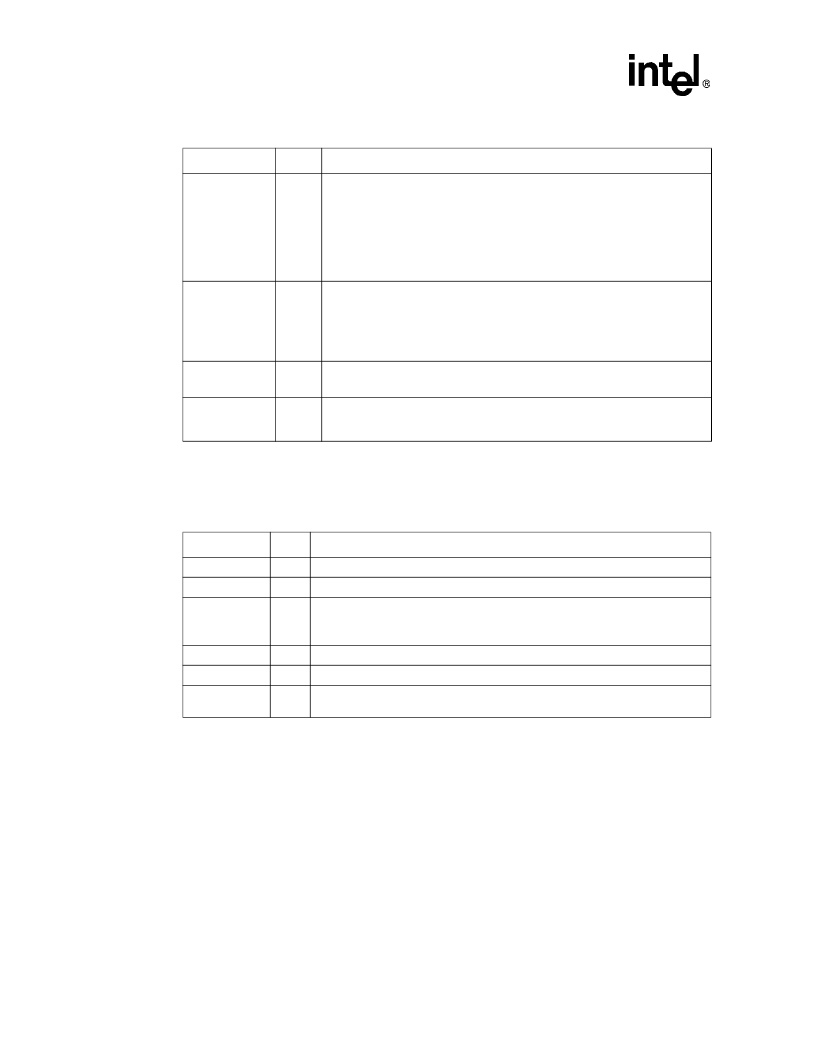

Table 23. SIU Interface

Signal Name

Type

Description

SIU_LAD[3:0]

I/O

SIU LPC Multiplexed Command, Address, Data

: Internal pull-ups are provided.

SIU_LCLK

I

SIU LPC clock input to SIU

: 33 MHz LPC clock.

SIU_LDRQ#

O

SIU LPC Serial DMA/Master Request Output

: Used by SIU devices to indicate a

DMA request.

NOTE:

These signals have weak internal pull-up resistors to avoid external glue.

SIU_LFRAME#

I

SIU LPC Frame

: Indicates the start of an LPC cycle, or an abort.

SIU_RESET#

I

SIU RESET

: This signal should be tied to PCI RESET.

SIU_SERIRQ

I/O

SIU Serial IRQ input

: This pin receives the serial interrupt protocol from external

devices. Pull up if unused.

Table 22. Universal Asynchronous Receive And Transmit (UART 0, 1) (Sheet 2 of 2)

Signal Name

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FWB150 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

| FWB151 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

| FWB1510 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

| FWB152 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

| FWB154 | 1.5 AMP FAST RECOVERY BRIDGE RECTIFIERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FW82801E S L5AW | 制造商:Intel 功能描述:I/O Controller Phase Controller 421-Pin BGA |

| FW82801EB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| FW82801EB S L6TN | 制造商:Intel 功能描述:CONTROLLER: IO CONTROLLER |

| FW82801EB S L73Z | 制造商:Intel 功能描述:I/O Controller Phase Controller 460-Pin BGA |

| FW82801ER | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。