- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370782 > HYB18T256324F-22 (INFINEON TECHNOLOGIES AG) 256-Mbit GDDR3 DRAM [600MHz] PDF資料下載

參數(shù)資料

| 型號: | HYB18T256324F-22 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 256-Mbit GDDR3 DRAM [600MHz] |

| 中文描述: | 256兆GDDR3顯示內(nèi)存[600MHz的] |

| 文件頁數(shù): | 57/80頁 |

| 文件大?。?/td> | 2026K |

| 代理商: | HYB18T256324F-22 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁當(dāng)前第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

HYB18T256324F–[16/20/22]

256-Mbit DDR SGRAM

Functional Description

Data Sheet

57

Rev. 1.11, 04-2005

10292004-DOXT-FS0U

3.9.1

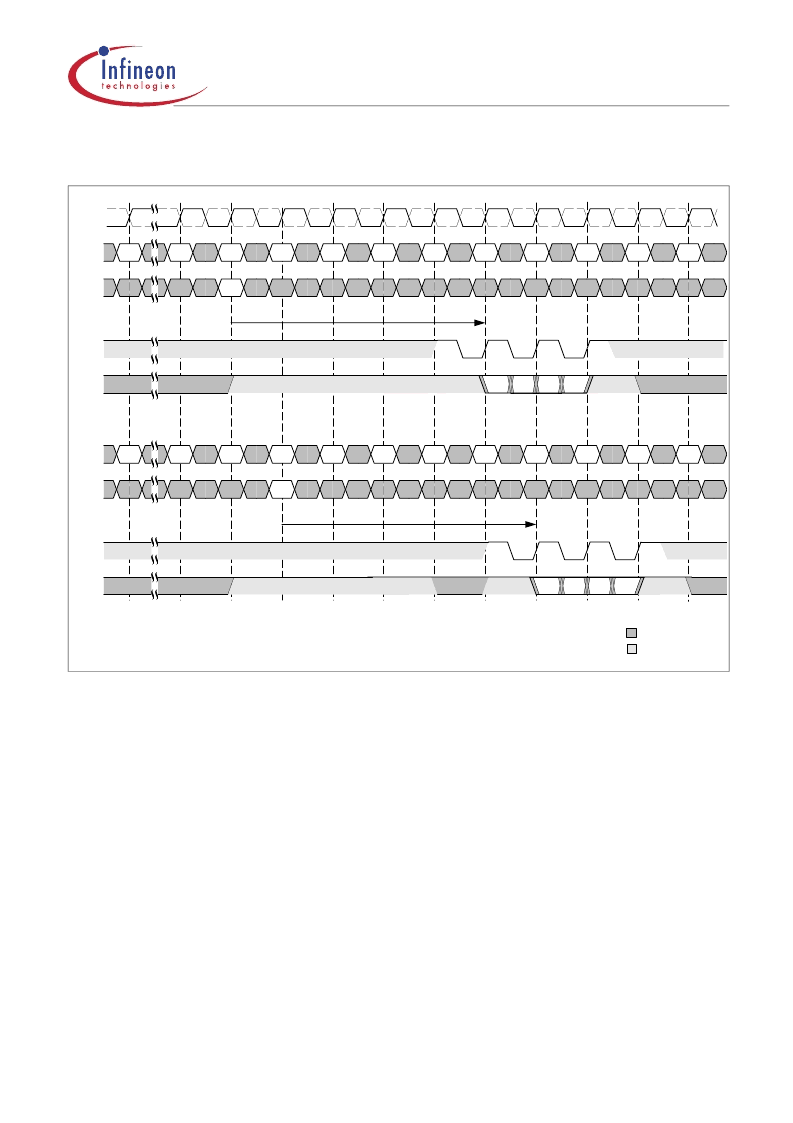

DTERDIS followed by READ

Figure 41

DTERDIS Command followed by READ

1. At least 3 NOPs are required between a DTERDIS command and a READ command in order to avoid

contention on the RDQS bus in a 2 rank system.

2. CAS Latency 5 is used as an example.

3. The DQ terminations are switched off (CL-1) clock periods after the DTERDIS command for a duration of 4

clocks.

#,+

#,+

. $

#OM

. $

. $

. $

. $

!DDR

#!3 LATENCY

. $

. $

$ONgT #ARE

" #X

2$

$4$

. $

"ANK #OLUMN ADDRESS X

2%!$

$4%2$)3

./0 OR $ESELECT

$X

$ATA FROM " #X

#OM

!DDR

#OMMAND

!DDRESS " #

$1S 4ERMINATIONS OFF

2$13 .OT DRIVEN

. $

. $

. $

2$13

$1

. $

#OM

. $

. $

. $

!DDR

#!3 LATENCY

. $

. $

. $

. $

. $

2$13

$1

. $

. $

. $

$X $ X $ X $ X

2$

2$

$X $ X $ X $ X

" #X

" #X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18T256400AFL-3 | 256 Mbi t DDR2 SDRAM |

| HYB18T256160A-3S | 256 Mbi t DDR2 SDRAM |

| HYB18T256800AFL-3 | 256 Mbi t DDR2 SDRAM |

| HYB18T256400AFL-37 | 256 Mbi t DDR2 SDRAM |

| HYB18T256800AFL-37 | 256 Mbi t DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18T256400AF-3.7 | 制造商:Infineon Technologies AG 功能描述:64M X 4 DDR DRAM, 0.5 ns, PBGA60 |

| HYB18T256400AF-5 | 制造商:Infineon Technologies AG 功能描述:SDRAM, DDR, 64M x 4, 60 Pin, Plastic, BGA |

| HYB18T256800AF-5 | 制造商:Infineon Technologies AG 功能描述: |

| HYB18T512161BF-25 | 制造商:Qimonda 功能描述:SDRAM, DDR, 32M x 16, 84 Pin, Plastic, BGA |

| HYB18T512400AF-5 | 制造商:Intersil Corporation 功能描述:SDRAM, DDR, 128M x 4, 60 Pin, Plastic, BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。