- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224103 > K4B4G0846B-MCF80 512M X 8 DDR DRAM, 0.3 ns, PBGA78 PDF資料下載

參數(shù)資料

| 型號: | K4B4G0846B-MCF80 |

| 元件分類: | DRAM |

| 英文描述: | 512M X 8 DDR DRAM, 0.3 ns, PBGA78 |

| 封裝: | HALOGEN FREE AND ROHS COMPLIANT, FBGA-78 |

| 文件頁數(shù): | 24/59頁 |

| 文件大小: | 1079K |

| 代理商: | K4B4G0846B-MCF80 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

Page 30 of 59

Rev. 1.0 March 2009

DDP 4Gb DDR3 SDRAM

K4B4G0446B

K4B4G0846B

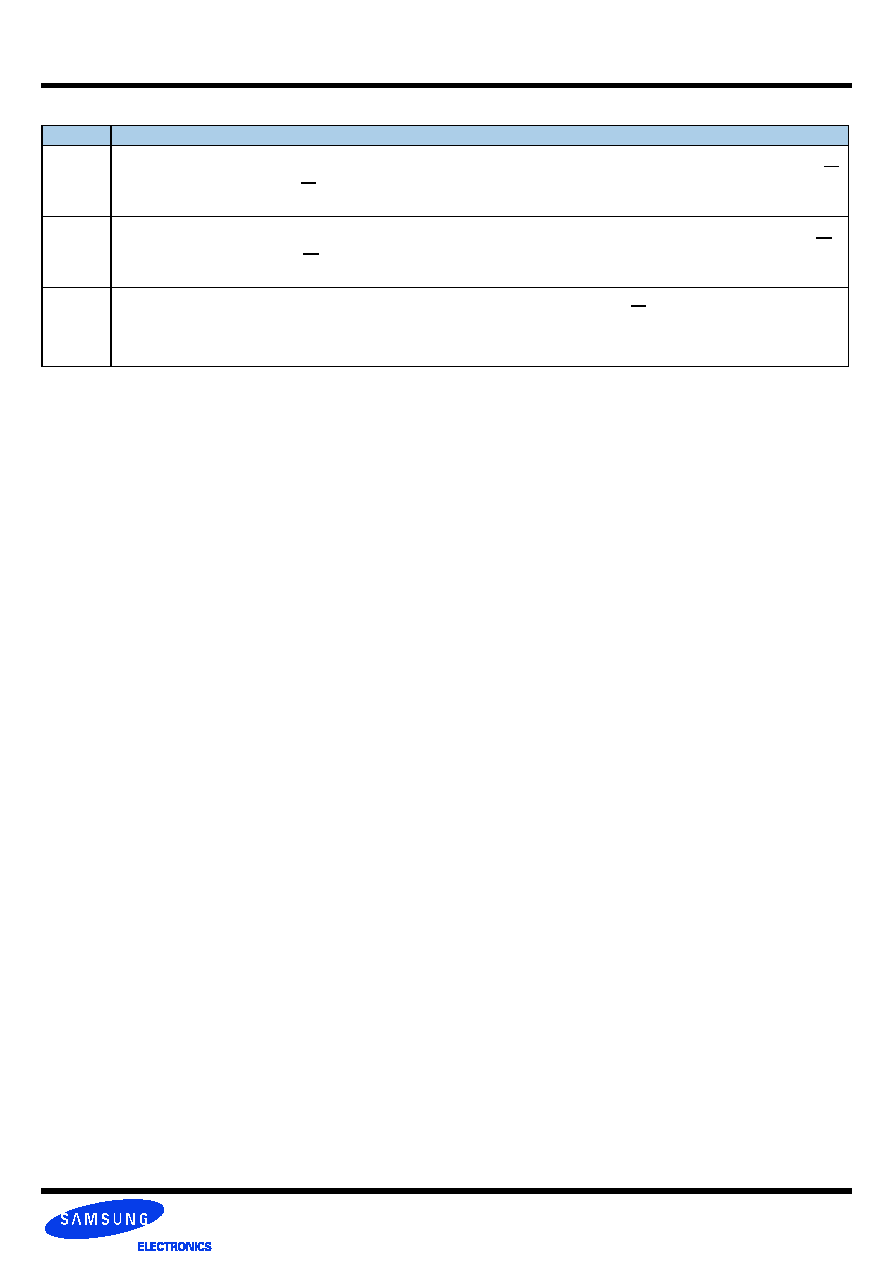

[ Table 31 ] Basic IDD and IDDQ Measurement Conditions

a) Burst Length: BL8 fixed by MRS: set MR0 A[1,0]=00B

b) Output Buffer Enable: set MR1 A[12] = 0B; set MR1 A[5,1] = 01B; RTT_Nom enable: set MR1 A[9,6,2] = 011B; RTT_Wr enable: set MR2 A[10,9] = 10B

c) Pecharge Power Down Mode: set MR0 A12=0B for Slow Exit or MR0 A12=1B for Fast Exit

d) Auto Self-Refresh (ASR): set MR2 A6 = 0B to disable or 1B to enable feature

e) Self-Refresh Temperature Range (SRT): set MR2 A7=0B for normal or 1B for extended temperature range

f) Refer to DRAM supplier data sheet and/or DIMM SPD to determine if optional features or requirements are supported by DDR3 SDRAM device

10.2 IDD Specifications definition

Editorial Instruction: Chapter 10.2 in JESD79-3B in principal stays at it is. See Reference Material at the end of this ballot.

Only the following changes will be done to Chapter 10.2:

Table 53 "IDD Specification Example 512M DDR3", add the following Rows:

- Between IDD2N and IDD2Q: Add 2 rows (one for x4/x8, one for x16) with a straddled cell for Symbol "IDD2NT".

- Between IDD2NT (as inserted with above bullet) and IDD2Q: Add 2 rows (one for x4/x8, one for x16) with a straddled cell for Symbol ’IDDQ2NT".

- Between IDD4R and IDD4W: Add 3 rows (one for x4, one for x8 and one for x16) with a straddled cell for Symbol "IDDQ4R".

Symbol

Description

IDD6ET

Self-Refresh Current: Extended Temperature Range (optional)f)

TCASE: 0 - 95°C; Auto Self-Refresh (ASR): Disabledd); Self-Refresh Temperature Range (SRT): Extendede); CKE: Low; External clock: Off; CK and CK:

LOW; CL: see Table 30 ; BL: 8a); AL: 0; CS, Command, Address, Bank Address, Data IO: MID-LEVEL;DM:stable at 0; Bank Activity: Extended Temperature

Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registersb); ODT Signal: MID-LEVEL

IDD6TC

Auto Self-Refresh Current (optional)f)

TCASE: 0 - 95°C; Auto Self-Refresh (ASR): Enabledd); Self-Refresh Temperature Range (SRT): Normale); CKE: Low; External clock: Off; CK and CK:

LOW; CL: see Table 30 ; BL: 8a); AL: 0; CS, Command, Address, Bank Address, Data IO: MID-LEVEL; DM:stable at 0; Bank Activity: Auto

Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registersb); ODT Signal: MID-LEVEL

IDD7

Operating Bank Interleave Read Current

CKE: High; External clock: On; tCK, nRC, nRAS, nRCD, nRRD, nFAW, CL: see Table 30 ; BL: 8a, g); AL: CL-1; CS: High between ACT and RDA; Command,

Address, Bank Address Inputs: partially toggling according to Table 39 ; Data IO: read data bursts with different data between one burst and the next one

according to Table 39 ; DM:stable at 0; Bank Activity: two times interleaved cycling through banks (0, 1, ...7) with different addressing, see Table 39 ; Output

Buffer and RTT: Enabled in Mode Registersb); ODT Signal: stable at 0; Pattern Details: see Table 39

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4E640411D-TC500 | 16M X 4 EDO DRAM, 50 ns, PDSO32 |

| K4F640411C-TC500 | 16M X 4 FAST PAGE DRAM, 50 ns, PDSO32 |

| K4F640412C-JC450 | 16M X 4 FAST PAGE DRAM, 45 ns, PDSO32 |

| K4T1G044QC-ZCLE6 | 256M X 4 DDR DRAM, 0.45 ns, PBGA60 |

| K4T56163QI-ZLD50 | 16M X 16 SYNCHRONOUS DRAM, 0.5 ns, PBGA84 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4B4G0846B-MCH9 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDP 4Gb B-die DDR3 SDRAM Specification |

| K4B4G0846D-BCK0000 | 制造商:Samsung Semiconductor 功能描述: |

| K4B4G1646B-HCH9000 | 制造商:Samsung Semiconductor 功能描述: |

| K4B4G1646B-HCK000 | 制造商:Samsung Semiconductor 功能描述: |

| K4B4G1646B-HCK0000 | 制造商:Samsung 功能描述:DDR SGRAM X16 TSOP2 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。