- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224103 > K4B4G0846B-MCF80 512M X 8 DDR DRAM, 0.3 ns, PBGA78 PDF資料下載

參數(shù)資料

| 型號: | K4B4G0846B-MCF80 |

| 元件分類: | DRAM |

| 英文描述: | 512M X 8 DDR DRAM, 0.3 ns, PBGA78 |

| 封裝: | HALOGEN FREE AND ROHS COMPLIANT, FBGA-78 |

| 文件頁數(shù): | 7/59頁 |

| 文件大?。?/td> | 1079K |

| 代理商: | K4B4G0846B-MCF80 |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

Page 15 of 59

Rev. 1.0 March 2009

DDP 4Gb DDR3 SDRAM

K4B4G0446B

K4B4G0846B

8.3 AC and DC Logic Input Levels for Ditterential Signals

8.3.1 Differential signal definition

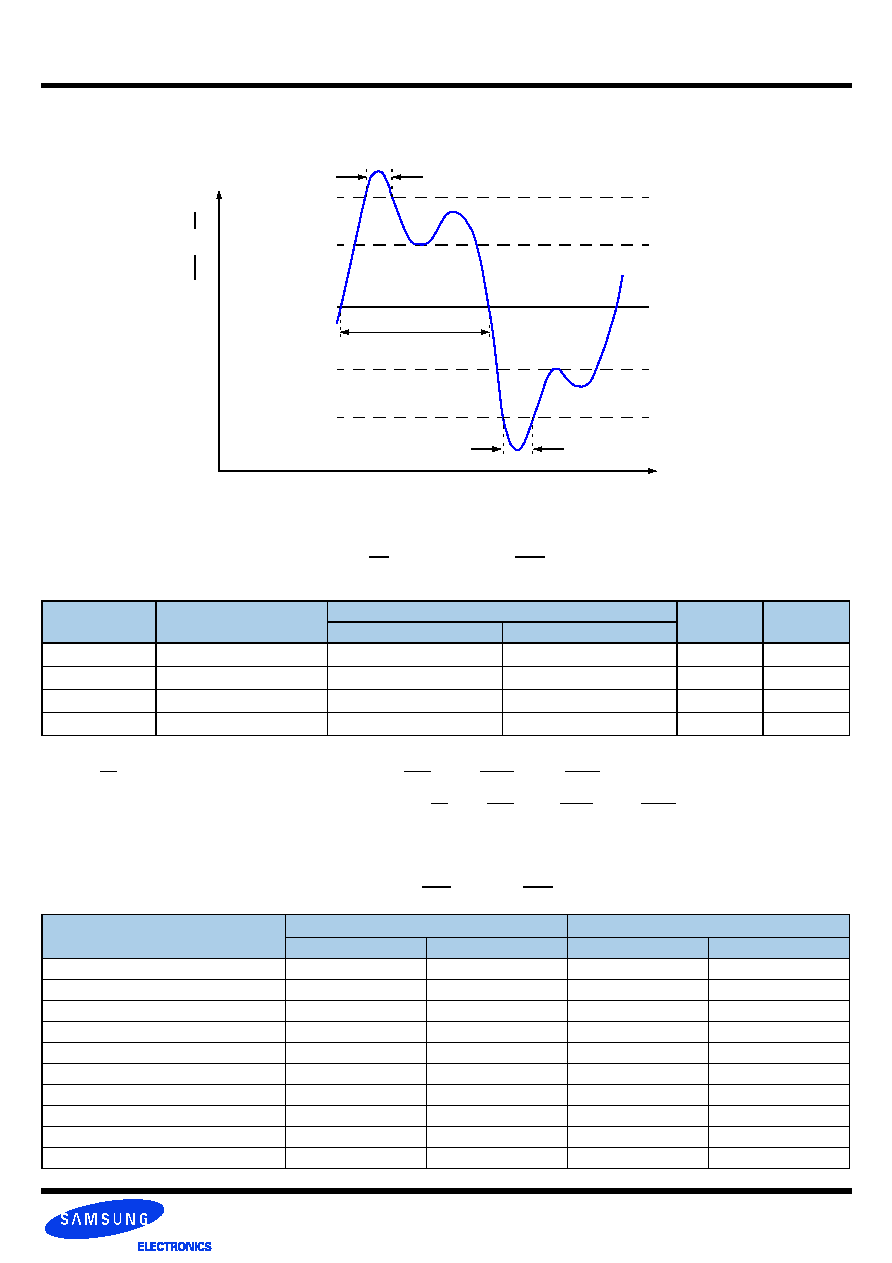

Figure 2 : Definition of differential ac-swing and "time above ac level" tDVAC

8.3.2 Differential swing requirement for clock (CK - CK) and strobe (DQS - DQS)

[ Table 9 ] Defferential AC and DC Input Levels

Notes:

1. Used to define a differential signal slew-rate.

2. for CK - CK use VIH/VIL(AC) of ADD/CMD and VREFCA; for DQS - DQS, DQSL - DQSL, DQSU - DQSU use VIH/VIL(AC) of DQs and VREFDQ; if a

reduced ac-high or ac-low level is used for a signal group, then the reduced level applies also here.

3. These values are not defined, however they single-ended signals CK, CK, DQS, DQS, DQSL, DQSL, DQSU, DQSU need to be within the respective

limits (VIH(DC) max, VIL(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot. Reter to "overshoot and Undersheet

Specification "

[ Table 10 ] Allowed time before ringback (tDVAC) for CLK - CLK and DQS - DQS

Symbol

Parameter

DDR3-800/1066/1333/1600

unit

Note

min

max

VIHdiff

differential input high

+0.2

note 3

V

1

VILdiff

differential input low

note 3

-0.2

V

1

VIHdiff(AC)

differential input high ac

2 x (VIH(AC)-VREF)

note 3

V

2

VILdiff(AC)

differential input low ac

note 3

2 x (VREF - VIL(AC))

V2

Slew Rate [V/ns]

tDVAC [ps] @ |VIH/Ldiff(AC)| = 350mV

tDVAC [ps] @ |VIH/Ldiff(AC)| = 300mV

min

max

min

max

> 4.0

75

-

175

-

4.0

57

-

170

-

3.0

50

-

167

-

2.0

38

-

163

-

1.8

34

-

162

-

1.6

29

-

161

-

1.4

22

-

159

-

1.2

13

-

155

-

1.0

0

-

150

-

< 1.0

0

-

150

-

0.0

tDVAC

VIH.DIFF.MIN

half cycle

Dif

feren

tia

lIn

put

V

o

lta

ge

(i

.e.

DQS-DQS

,CK-CK

)

time

tDVAC

VIH.DIFF.AC.MIN

VIL.DIFF.MAX

VIL.DIFF.AC.MAX

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4E640411D-TC500 | 16M X 4 EDO DRAM, 50 ns, PDSO32 |

| K4F640411C-TC500 | 16M X 4 FAST PAGE DRAM, 50 ns, PDSO32 |

| K4F640412C-JC450 | 16M X 4 FAST PAGE DRAM, 45 ns, PDSO32 |

| K4T1G044QC-ZCLE6 | 256M X 4 DDR DRAM, 0.45 ns, PBGA60 |

| K4T56163QI-ZLD50 | 16M X 16 SYNCHRONOUS DRAM, 0.5 ns, PBGA84 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4B4G0846B-MCH9 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDP 4Gb B-die DDR3 SDRAM Specification |

| K4B4G0846D-BCK0000 | 制造商:Samsung Semiconductor 功能描述: |

| K4B4G1646B-HCH9000 | 制造商:Samsung Semiconductor 功能描述: |

| K4B4G1646B-HCK000 | 制造商:Samsung Semiconductor 功能描述: |

| K4B4G1646B-HCK0000 | 制造商:Samsung 功能描述:DDR SGRAM X16 TSOP2 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。