- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄367908 > pentium III (Intel Corp.) pentium III Processor for the PGA370 Socket at 500MHz to 933MHz(工作頻率500到933兆赫茲活動(dòng)帶PGA370插孔奔III處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | pentium III |

| 廠商: | Intel Corp. |

| 英文描述: | pentium III Processor for the PGA370 Socket at 500MHz to 933MHz(工作頻率500到933兆赫茲活動(dòng)帶PGA370插孔奔III處理器) |

| 中文描述: | 奔騰III處理器在500MHz到933MHz的(工作頻率500到933兆赫茲活動(dòng)帶PGA370插孔奔三處理器的PGA370插座) |

| 文件頁(yè)數(shù): | 44/78頁(yè) |

| 文件大小: | 610K |

| 代理商: | PENTIUM III |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)當(dāng)前第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)

44

Datasheet

Pentium

III Processor for the PGA370 Socket at 500 MHz to 933 MHz

3.4.1

Overshoot/Undershoot Guidelines

Overshoot (or undershoot) is the absolute value of the maximum voltage above the nominal high

voltage or below V

SS

. The overshoot guideline limits transitions beyond V

CC

or V

SS

due to the fast

signal edge rates (see

Figure 17

for non-AGTL+ signals). The processor can be damaged by

repeated overshoot events on 1.5 V or 2.5 V tolerant buffers if the charge is large enough (i.e., if

the overshoot is great enough). Permanent damage to the processor is the likely result of excessive

overshoot/undershoot. Violating the overshoot/undershoot guideline will also make satisfying the

ringback specification difficult.

The overshoot/undershoot guideline is 0.3 V

and assumes the

absence of diodes on the input. These guidelines should be verified in simulations

without the on-

chip ESD protection diodes present

because the diodes will begin clamping the 1.5 V and 2.5 V

tolerant signals beginning at approximately 0.7 V above the appropriate supply and 0.7 V below

V

SS

. If signals are not reaching the clamping voltage, this will not be an issue. A system should not

rely on the diodes for overshoot/undershoot protection as this will negatively affect the life of the

components and make meeting the ringback specification very difficult.

Note:

The undershoot guideline limits transitions exactly as described for the ATGL+ signals. See

Figure 16

.

3.4.2

Ringback Specification

Ringback refers to the amount of reflection seen after a signal has switched. The ringback

specification is the voltage that the signal rings back to after achieving its maximum absolute

value. See

Figure 17

for an illustration of ringback. Excessive ringback can cause false signal

detection or extend the propagation delay. The ringback specification applies to the input pin of

each receiving agent. Violations of the signal ringback specification are not allowed under any

circumstances for non-AGTL+ signals.

Ringback can be simulated with or without the input protection diodes that can be added to the

input buffer model. However, signals that reach the clamping voltage should be evaluated further.

See

Table 23

for the signal ringback specifications for non-AGTL+ signals for simulations at the

processor pins.

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all Pentium III processor frequencies.

2. Non-AGTL+ signals except PWRGOOD.

3.4.3

Settling Limit Guideline

Settling limit defines the maximum amount of ringing at the receiving pin that a signal must reach

before its next transition. The amount allowed is 10% of the total signal swing (V

HI

–

V

LO

) above

and below its final value. A signal should be within the settling limits of its final value, when either

in its high state or low state, before it transitions again.

Signals that are not within their settling limit before transitioning are at risk of unwanted

oscillations which could jeopardize signal integrity. Simulations to verify settling limit may be

done either with or without the input protection diodes present. Violation of the settling limit

guideline is acceptable if simulations of 5 to 10 successive transitions do not show the amplitude of

the ringing increasing in the subsequent transitions.

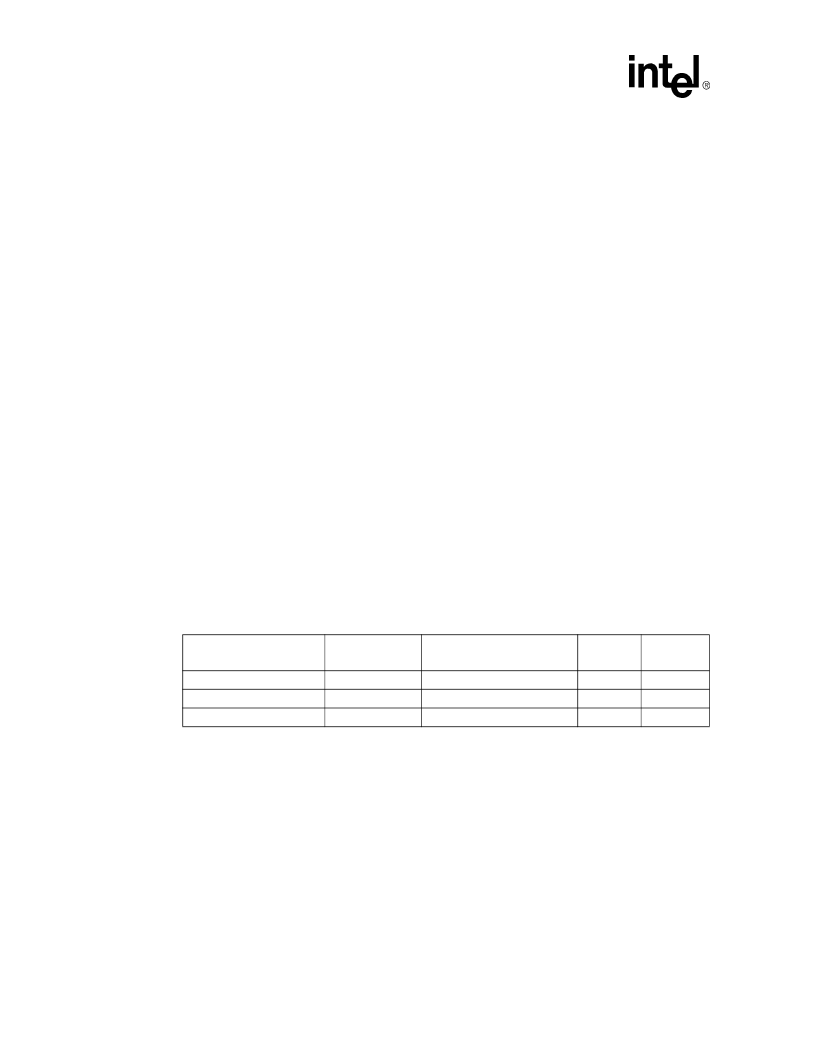

Table 23. Signal Ringback Specifications for Non-AGTL+ Signal Simulation at the Processor

Pins

1

Input Signal Group

Transition

Maximum Ringback

(with Input Diodes Present)

Unit

Figure

Non-AGTL+ Signals

2

Non-AGTL+ Signals

2

0

→

1

1

→

0

0

→

1

Vref + 0.200

V

17

Vref - 0.200

V

17

PWRGOOD

2.00

V

17

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pentium II | pentium II processor With On-die Cache Mobile Module Connector 1 (MMC-1)(帶緩存和連接器1的奔II處理器) |

| PERICOMPI7C8150 | 2-Port PCI-to-PCI Bridge |

| PESDXL2BT | Low capacitance double bidirectional ESD protection diodes in SOT23 |

| PESDXL2UM | LJT 23C 21#20 2#16 PIN RECP |

| PETAM1270BK300R | BRAID SLEEVING 300M |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。