- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359412 > VPX3224D (Electronic Theatre Controls, Inc.) Video Pixel Decoders PDF資料下載

參數(shù)資料

| 型號: | VPX3224D |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Video Pixel Decoders |

| 中文描述: | 視頻解碼器像素 |

| 文件頁數(shù): | 23/92頁 |

| 文件大小: | 672K |

| 代理商: | VPX3224D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

23

Micronas

2.8. Video Reference Signals

The complete video interface of the VPX runs at a clock

rate of 13.5 MHz. It mainly generates two reference sig-

nals for the video timing: a horizontal reference (HREF)

and a vertical reference (VREF). These two signals are

generated by programmable hardware and can be ei-

ther free running or synchronous to the analog input vid-

eo. The video line standard (625/50 or 525/60) depends

on the TV-standard selected with FP-RAM 0x20 [sdt].

The polarity of both signals is individually selectable via

FP-RAM 0x153.

The circuitry which produces the VREF and HREF sig-

nals has been designed to provide a stable, robust set

of timing signals, even in the case of erratic behavior at

the analog video input. Depending on the selected oper-

ating mode given in FP-RAM 0x140 [settm], the period

of the HREF and VREF signals are guaranteed to re-

main within a fixed range. These video reference signals

can therefore be used to synchronize the external com-

ponents of a video subsystem (for example the ICs of a

PC add-in card).

In addition to the timing references, valid video samples

are marked with the ‘video active’ qualifier (VACT). In or-

der to reduce the signal number of the video interface,

several 8-bit modes have been implemented, where the

reference signals are multiplexed into the data stream

(see section 2.6.1.).

2.8.1. HREF

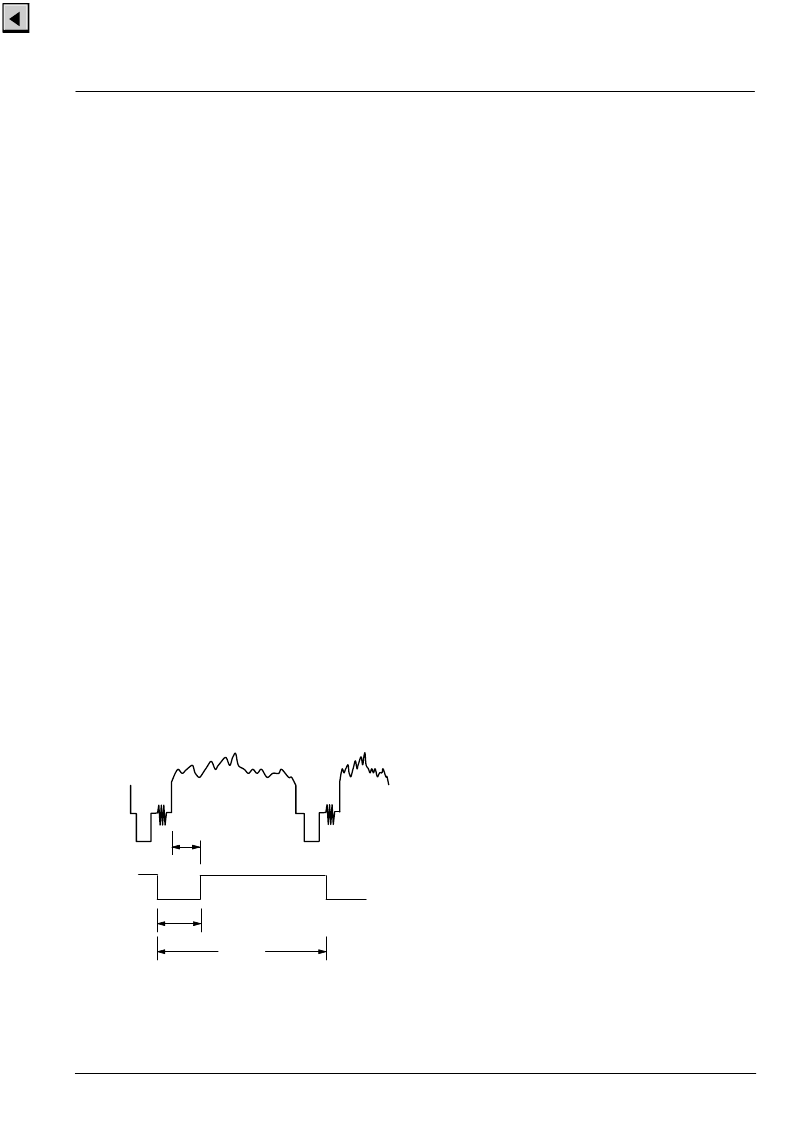

Fig. 2–26 illustrates the timing of the HREF signal rela-

tive to the analog input. The inactive period of HREF has

a fixed length of 64 periods of the 13.5 MHz output clock

rate. The total period of the HREF signal is expressed as

nominal

and depends on the video line standard.

Analog

Video

Input

HREF

VPX

Delay

Fig. 2–26:

HREF relative to input video

4.7

μ

s (64 cycles)

nominal

2.8.2. VREF

Figs. 2–27 and 2–28 illustrate the timing of the VREF

signal relative to field boundaries of the two TV stan-

dards. The start of the VREF pulse is fixed, while the

length is programmable in the range between 2 and 9

video lines via FP-RAM 0x153 [vlen].

2.8.3. Odd/Even Information (FIELD)

Information on whether the current field is odd or even

is supplied through the relationship between the edge

(either leading or trailing) of VREF and level of HREF.

This relationship is fixed and shown in Figs. 2–27 and

2–28. The same information can be supplied to the

FIELD pin, which can be enabled/disabled as output in

FP-RAM 0x153 [enfieldq]. FP-RAM 0x153 [oepol] pro-

grams the polarity of this signal.

During normal operation the FIELD flag is filtered since

most applications need interlaced signals. After filtering,

the field type is synchronized to the input signal only if

the last 8 fields have been alternating; otherwise, it al-

ways toggles. This filtering can be disabled with FP-

RAM 0x140 [disoef]. In this case, the field information

follows the odd/even property of the input video signal.

相關PDF資料 |

PDF描述 |

|---|---|

| VPX3224E | Video Pixel Decoders |

| VPX322XE | Video Pixel Decoders |

| VQ1000J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓60V,夾斷電流0.225A的N溝道增強型MOSFET晶體管) |

| VQ1000J | N-Channel 60-V (D-S) MOSFET |

| VQ1001J | Dual N-Channel 30-V (D-S) MOSFET with Schottky Diode |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| VPX3224D-C3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| VPX3224E | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Pixel Decoders |

| VPX3225D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Pixel Decoders |

| VPX3225D-C3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| VPX3225E | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Pixel Decoders |

發(fā)布緊急采購,3分鐘左右您將得到回復。