- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359412 > VPX3224D (Electronic Theatre Controls, Inc.) Video Pixel Decoders PDF資料下載

參數(shù)資料

| 型號: | VPX3224D |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Video Pixel Decoders |

| 中文描述: | 視頻解碼器像素 |

| 文件頁數(shù): | 35/92頁 |

| 文件大小: | 672K |

| 代理商: | VPX3224D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

35

Micronas

2.14. Control Interface

2.14.1. Overview

Communication between the VPX and the external con-

troller is performed serially via the I

2

C bus (pins SCL and

SDA).

There are basically two classes of registers in the VPX.

The first class of registers are the directly addressable

I

2

C registers. These are registers embedded directly in

the hardware. Data written to these registers is inter-

preted combinatorially directly by the hardware. These

registers are all a maximum of 8-bits wide.

The second class of registers are the ‘FP-RAM regis-

ters’, the memory of the onboard microcontroller (Micro-

nas Fast Processor). Data written into this class of regis-

ters is read and interpreted by the FP’s micro-code.

Internally, these registers are 12 bits wide. Communica-

tions with these registers require I

2

C packets with 16-bit

data payloads.

Communication with both classes of registers (I

2

C and

FP-RAM) is performed via I

2

C. The format of the I

2

C

telegram depends on which type of register is being ad-

dressed.

2.14.2. I

2

C Bus Interface

The VPX has an I

2

C bus slave interface and uses I

2

C

clock synchronization to slow down the interface if re-

quired. The I

2

C bus interface uses one level of subad-

dressing. First, the bus address selects the IC, then a

subaddress selects one of the internal registers.

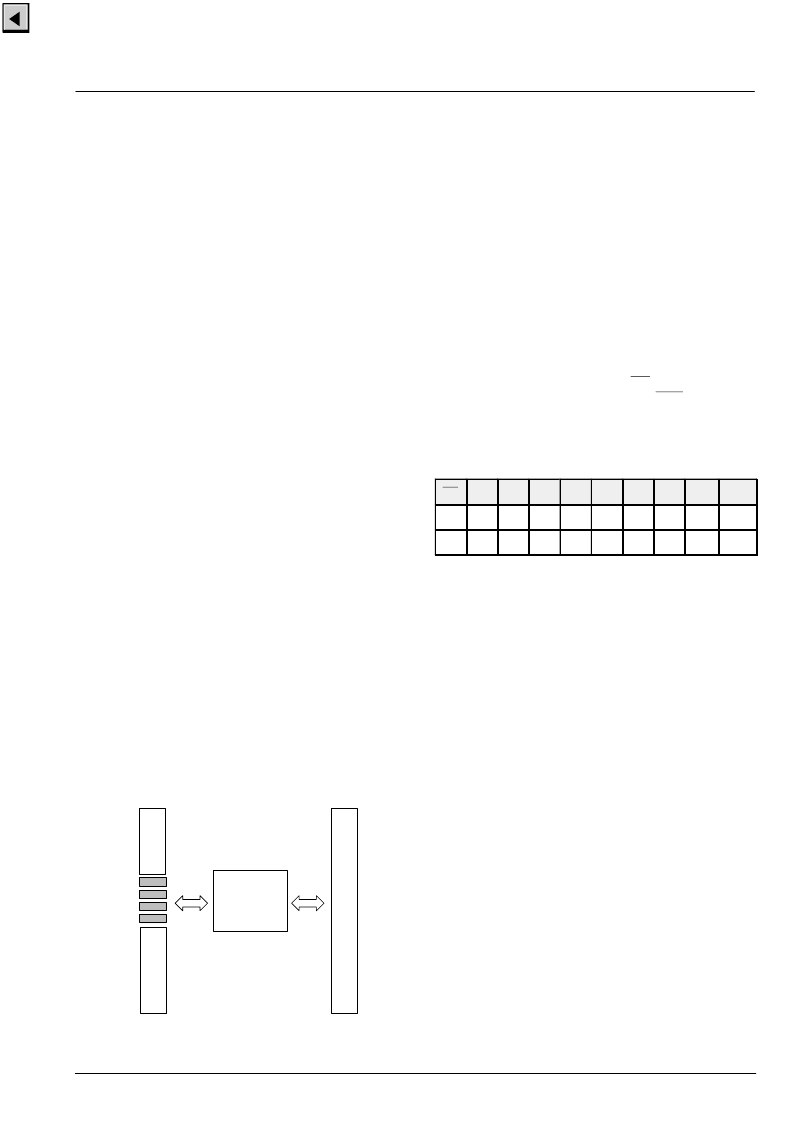

FP

controller

Read Address

Write Address

Data

Status

I

2

C

subaddress

space

0

FP-RAM

0

Fig. 2–39:

FP register addressing

ff

17f

The I

2

C interface of the VPX conforms to the I

2

C bus

specification for the fast-mode. It incorporates slope

control for the falling edges of the SDA and SCL signals.

If the power supply of the VPX is switched off, both pins

SCL and SDA float. External pull-up devices must be

adapted to fulfill the required rise time for the fast-mode.

For bus loads up to 200 pF, the pull-up device could be

a resistor; for bus loads between 200 pF and 400 pF, the

pull-up device can be a current source (3 mA max.) or

a switched resistor circuit.

2.14.3. Reset and I

2

C Device Address Selection

The VPX can respond to one of two possible chip ad-

dresses. The address selection is made at reset by an

externally supplied level on the OE pin. This level is

latched on the inactive going edge of RES.

Table 2–15:

I

2

C bus device addresses

OE

A6

A5

A4

A3

A2

A1

A0

R/W

hex

0

1

0

0

0

0

1

1

1/0

86/87

1

1

0

0

0

1

1

1

1/0

8e/8f

2.14.4. Protocol Description

Once the reset is complete, the IC is selected by assert-

ing the device address in the address part of a I

2

C trans-

mission. A device address pair is defined as a write ad-

dress (86 hex or 8e hex) and a read address (87 hex or

8f hex). Writing is done by sending the device write ad-

dress first, followed by the subaddress byte and one or

two data bytes. For reading, the read subaddress has to

be transmitted, first, by sending the device write address

(86 hex or 8e hex) followed by the subaddress, a second

start condition with the device read address (87 hex or

8f hex), and reading one or two bytes of data. It is not al-

lowed to send a stop condition in between. This will re-

sult in reading erratic data.

The registers of the VPX have 8 or 16 bit data size; 16-bit

registers are accessed by reading/writing two 8-bit data

bytes with the high byte first. The order of the bits in a

data/address/subaddress byte is always MSB first.

Figure 2–40 shows I

2

C bus protocols for read and write

operations of the interface; the read operation requires

an extra start condition after the subaddress and repeti-

tion of the read chip address, followed by the read data

bytes. The following protocol examples use device ad-

dress hex 86/87.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VPX3224E | Video Pixel Decoders |

| VPX322XE | Video Pixel Decoders |

| VQ1000J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓60V,夾斷電流0.225A的N溝道增強(qiáng)型MOSFET晶體管) |

| VQ1000J | N-Channel 60-V (D-S) MOSFET |

| VQ1001J | Dual N-Channel 30-V (D-S) MOSFET with Schottky Diode |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPX3224D-C3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| VPX3224E | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Pixel Decoders |

| VPX3225D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Pixel Decoders |

| VPX3225D-C3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| VPX3225E | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Pixel Decoders |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。