- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359412 > VPX3224D (Electronic Theatre Controls, Inc.) Video Pixel Decoders PDF資料下載

參數(shù)資料

| 型號: | VPX3224D |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Video Pixel Decoders |

| 中文描述: | 視頻解碼器像素 |

| 文件頁數(shù): | 83/92頁 |

| 文件大?。?/td> | 672K |

| 代理商: | VPX3224D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁當(dāng)前第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

83

Micronas

7. Application Notes

7.1. Differences between VPX 3220A and VPX 322xD

The following items indicate the differences between the

VPX 322xD and the VPX 3220A:

Internal

– The control registers (I

2

C and FP-RAM) contain signif-

icant changes.

– VPX 322xD incorporates a text slicer. Furthermore,

raw ADC data is supported (sampling frequency of

20.25 MHz/8 bit, output data rate 13.5 MHz/16 bit).

– VPX 322xD does not support RGB and compressed

video data output formats. The VPX 322xD supports

ITU-R601 and ITU-R656.

– The VPX 322xD does not provide an asynchronous

output mode, PIXCLK functions as an output only. The

VPX 322xD supports half-clock data rate (6.75 MHz).

– The VPX 322xD does not provide a video data rate of

20.25 MHz at the output interface.

– The VPX 322xD has an implemented low power

mode.

External

– Power-up Default Selection

Selection

VPX 3220A

VPX 322xD

I

2

C device

address

PREF

OE

wake-up default

Pads tristate/

active

PIXCLK

FIELD

– The VPX 322xD does not use the internal I

2

C bus for

power-up initialization. Resultingly, the I

2

C interface

will not be locked during that period.

– The VPX 322xD supports an 8-bit programmable out-

put port if the device uses only A[7:0] for video data

output.

– The VPX 322xD provides a HREF signal with a fixed

low period, whereas the width of the high period will

vary while the video input signal varies.

7.2. Impact to Signal to Noise Ratio

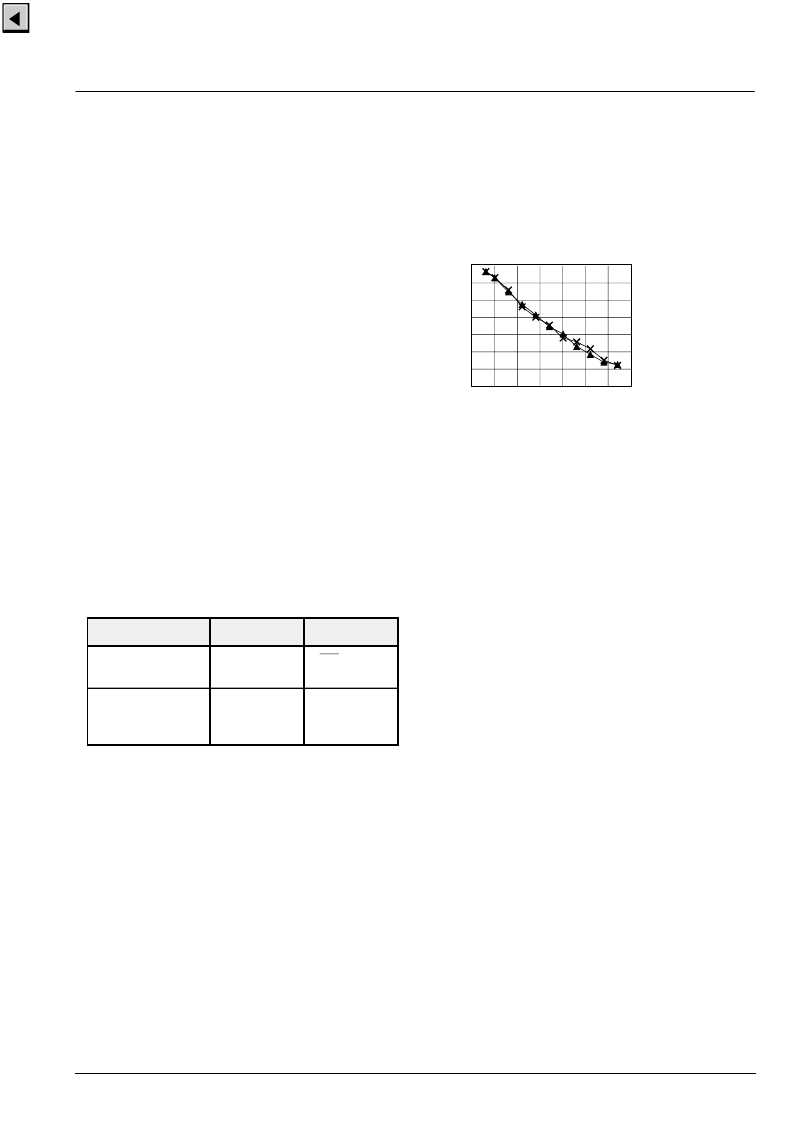

Fig. 7–1 shows the impact of the variation of the power

supply with respect to the SNR of the ADCs. The noise

due to the digital output interface leads to an impact of

the analog performance of the analog ADCs. Application

engineers should minimize load capacitances and driver

strength of the output signals.

38

39

40

41

42

43

44

45

2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0

S

PVDD [V]

Fig. 7–1:

Dependency between SNR and

Power Supply

Note:

Both ADCs are working and routed to A[7:0], and

B[7:0]. All interfaces are working with maximum driver

strength bandwidth measurement is performed up to 5

MHz.

7.3. Control Interface

7.3.1. Symbols

<

>

aa

dd

Start Condition

Stop Condition

(Sub-)Address Byte

Data Byte

7.3.2. Write Data into I

2

C Register

<86 f2 dd>

write to register OENA

7.3.3. Read Data from I

2

C Register

<86 00 <87 dd>

read Manufacture ID

7.3.4. Write Data into FP Register

<86 35 <87 dd>

<86 37 aa aa>

<86 35 <87 dd>

<86 38 dd dd>

poll busy bit[2] until it is cleared

write FP register write address

poll busy bit[2] until it is cleared

write data into FP register

7.3.5. Read Data from FP Register

<86 35 <87 dd>

<86 36 aa aa>

<86 35 <87 dd>

<86 38 <87 dd dd>

read data from FP register

poll busy bit[2] until it is cleared

write FP register read address

poll busy bit[2] until it is cleared

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VPX3224E | Video Pixel Decoders |

| VPX322XE | Video Pixel Decoders |

| VQ1000J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓60V,夾斷電流0.225A的N溝道增強型MOSFET晶體管) |

| VQ1000J | N-Channel 60-V (D-S) MOSFET |

| VQ1001J | Dual N-Channel 30-V (D-S) MOSFET with Schottky Diode |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPX3224D-C3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| VPX3224E | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Pixel Decoders |

| VPX3225D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Pixel Decoders |

| VPX3225D-C3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| VPX3225E | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Pixel Decoders |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。