- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359412 > VPX3224D (Electronic Theatre Controls, Inc.) Video Pixel Decoders PDF資料下載

參數(shù)資料

| 型號(hào): | VPX3224D |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Video Pixel Decoders |

| 中文描述: | 視頻解碼器像素 |

| 文件頁(yè)數(shù): | 69/92頁(yè) |

| 文件大?。?/td> | 672K |

| 代理商: | VPX3224D |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)當(dāng)前第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

VPX 3225D, VPX 3224D

PRELIMINARY DATA SHEET

69

Micronas

I

2

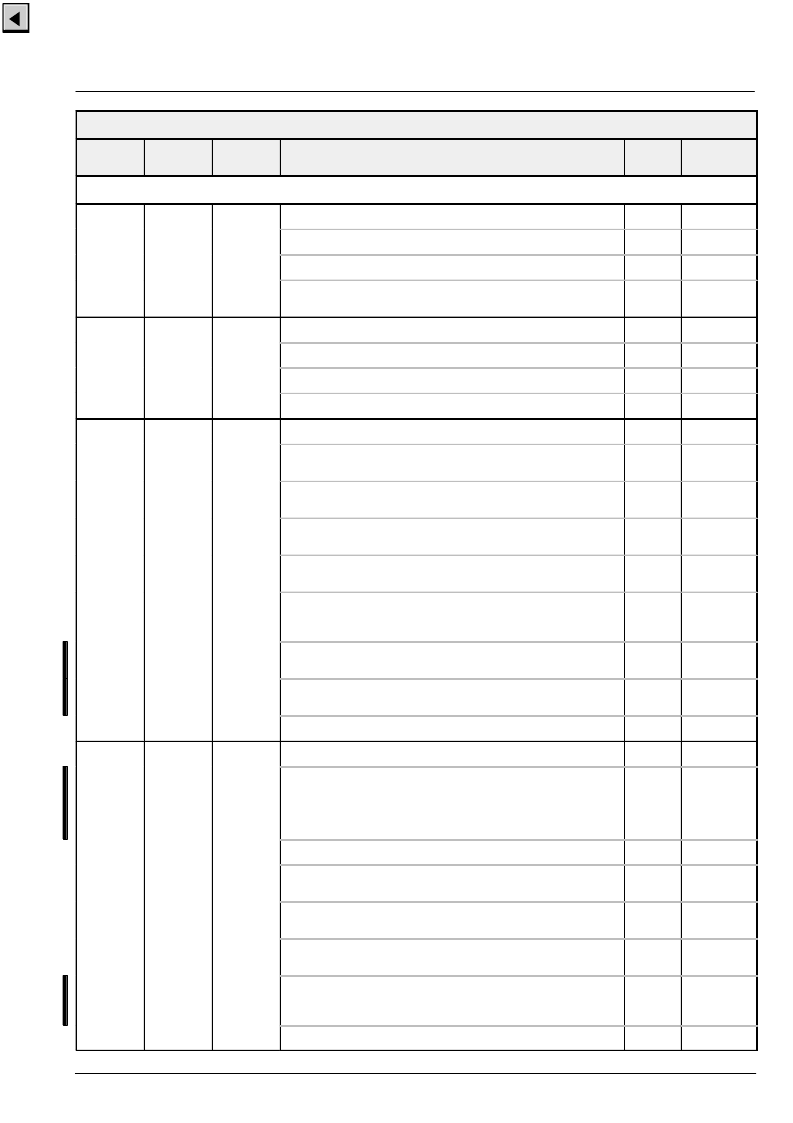

C-Registers VPX Back-End

Name

Default

Function

Mode

Number

of bits

Address

Hex

Output

h’F8

8

w

Pad Driver Strength – TTL Output Pads Typ A

DRIVER_A

bit [2:0] :

Driver strength of Port A[7:0]

stra1

bit [5:3] :

Driver strength of PIXCLK, LLC, and VACT

stra2

bit [7:6] :

additional PIXCLK driver strength

strength = bit [5:3] | {bit [7:6], 0}

stra3

h’F9

8

w

Pad Driver Strength – TTL Output Pads Typ B

DRIVER_B

bit [2:0] :

Driver strength of Port B[7:0]

strb1

bit [5:3] :

Driver strength of HREF, VREF, FIELD, and LLC2

strb2

bit [7:6] :

reserved (must be set to zero)

h’F2

8

w

Output Enable

OENA

direct

bit [0] :

1

0

Enable Video Port A

Disable / High Impedance Mode

aen

direct

bit [1] :

1

0

Enable Video Port B

Disable / High Impedance Mode

ben

direct

bit [2] :

1

0

Enable Pixclk Output

Disable / High Impedance Mode

clken

direct

bit [3] :

1

0

Enable HREF, VREF, FIELD, VACT, LLC, LLC2

Disable / High Impedance Mode

zen

direct

bit[4]

1

Enable LLC2 to TDO pin

(if JTAG interface is in Test-Logic-Reset State)

Disable LLC2

0

llc2en

direct

bit [5] :

1

0

no delay of OEQ input signal

1 LLC cycle delay of OEQ input signal (if bit [6] = 1)

oeqdel

direct

bit [6] :

1

0

latch OEQ input signal with rising edge of LLC

don’t latch OEQ input signal

latoeq

direct

bit [7] :

1

disable OEQ pin function

oeq_dis

h’AA

8

w

Low power mode, LLC mode

LLC

bit [1:0] :

Low power mode

active mode, outputs enabled

outputs tri-stated; clock divided by 2, I

2

C full speed

outputs tri-stated; clock divided by 4, I

2

C full speed

outputs tri-stated; clock divided by 8, I

2

C < 100 kbit/s

00

01

10

11

lowpow

bit [2] :

I

2

C reset

iresen

bit [3] :

1

0

connect LLC2 to TDO pin

connect bit[4] to TDO pin

llc2

bit [4] :

if bit[3] then bit[4] defines LLC2 polarity

else bit[4] is connected to TDO pin

llc2_pol

bit [5] :

switch-off slicer

(if slowpow = 1 then all slicer registers are reset).

slowpow

bit [6] :

1

0

use old llc timing with long hold time

use new llc timing with shorter hold time

(version D4 only)

oldllc

bit [7] :

reserved (must be set to zero)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VPX3224E | Video Pixel Decoders |

| VPX322XE | Video Pixel Decoders |

| VQ1000J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓60V,夾斷電流0.225A的N溝道增強(qiáng)型MOSFET晶體管) |

| VQ1000J | N-Channel 60-V (D-S) MOSFET |

| VQ1001J | Dual N-Channel 30-V (D-S) MOSFET with Schottky Diode |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPX3224D-C3 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microprocessor |

| VPX3224E | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Video Pixel Decoders |

| VPX3225D | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Video Pixel Decoders |

| VPX3225D-C3 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microprocessor |

| VPX3225E | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Video Pixel Decoders |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。