- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1909 > CS8952-IQZ (Cirrus Logic Inc)IC TXRX 100/10 PHY 100TQFP PDF資料下載

參數(shù)資料

| 型號: | CS8952-IQZ |

| 廠商: | Cirrus Logic Inc |

| 文件頁數(shù): | 69/81頁 |

| 文件大小: | 0K |

| 描述: | IC TXRX 100/10 PHY 100TQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 類型: | 收發(fā)器 |

| 規(guī)程: | MII |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LQFP |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP(14x14) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 759 (CN2011-ZH PDF) |

| 其它名稱: | 598-1208 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁當(dāng)前第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁

CS8952

CrystalLAN 100BASE-X and 10BASE-T Transceiver

71

DS206F1

When the TCM pin is high on power-up or reset, the CLK25 pin may be used as a source for the

TX_CLK pin. When the TCM pin is floating on power-up or reset, TX_CLK must be supplied externally.

TX_CLK should have the following nominal frequency:

TX_EN - Transmit Enable. Input, Pin 43.

Asserted high to indicate valid data nibbles are present on TXD[3:0]. When BPALIGN is selected,

TX_EN must be pulled up to VDD_MII.

TX_ER/TXD4 - Transmit Error Encoding/Transmit Data 4. Input, Pin 38.

When high, TX_ER indicates to the CS8952 that a transmit error has occurred. If TX_ER is asserted

simultaneously with TX_EN in 100 Mb/s mode, the CS8952 will ignore the data on the TXD[3:0] pins

and transmit one or more 100 Mb/s HALT symbols in its place. In 10 Mb/s mode, TX_ER has no effect

on the transmitted data.

If BP4B5B or BPALIGN are set, TX_ER/TXD4 is used to transmit the most-significant bit of the five-bit

code group.

TXD[3:0] - Transmit Data. Input, Pins 47, 46, 45, and 44.

Transmit data input pins. For MII modes, nibble-wide data (synchronous to TX_CLK) must be presented

on pins TXD[3:0] when TX_EN is asserted high. TXD0 is the least significant bit. In 10 Mb/s serial

mode, pin TXD0 is used as the serial input pin, and TXD[3:1] are ignored.

When either BP4B5B or BPALIGN is selected, pin TXD4 contains the most significant bit of the five-bit

code-group.

Control and Status Pins

10BT_SER - 10 Mb/s Serial Mode Select. Input, Pin 23.

When asserted high during power-up or reset and 10 Mb/s operation is selected, serial data will be

transferred on pins RXD0 and TXD0. When low during power-up or reset and 10 Mb/s operation is

selected, data is transferred a nibble at a time on RXD[3:0] and TXD[3:0]. This pin is ignored during

100 Mb/s operation.

10 Mb/s serial mode may also be entered under software control through bit 9 of the 10BASE-T Status

Register (address 1Bh).

At power-up or at reset, the value on this pin is latched into bit 9 of the 10BASE-T Status Register

(address 1Bh). This pin includes a weak internal pull-down (> 20 k

), or the value may be set by an

external 4.7 k

pull-up or pull-down resistor.

AN[1:0] - Auto-Negotiate Control. Input, Pins 58 and 57.

These three-level input pins are sampled during power-up or reset. They control the forced or

advertised auto-negotiation operating modes. If one of these pins is left unconnected, internal logic pulls

its signal to a mid-range value, 'M'.

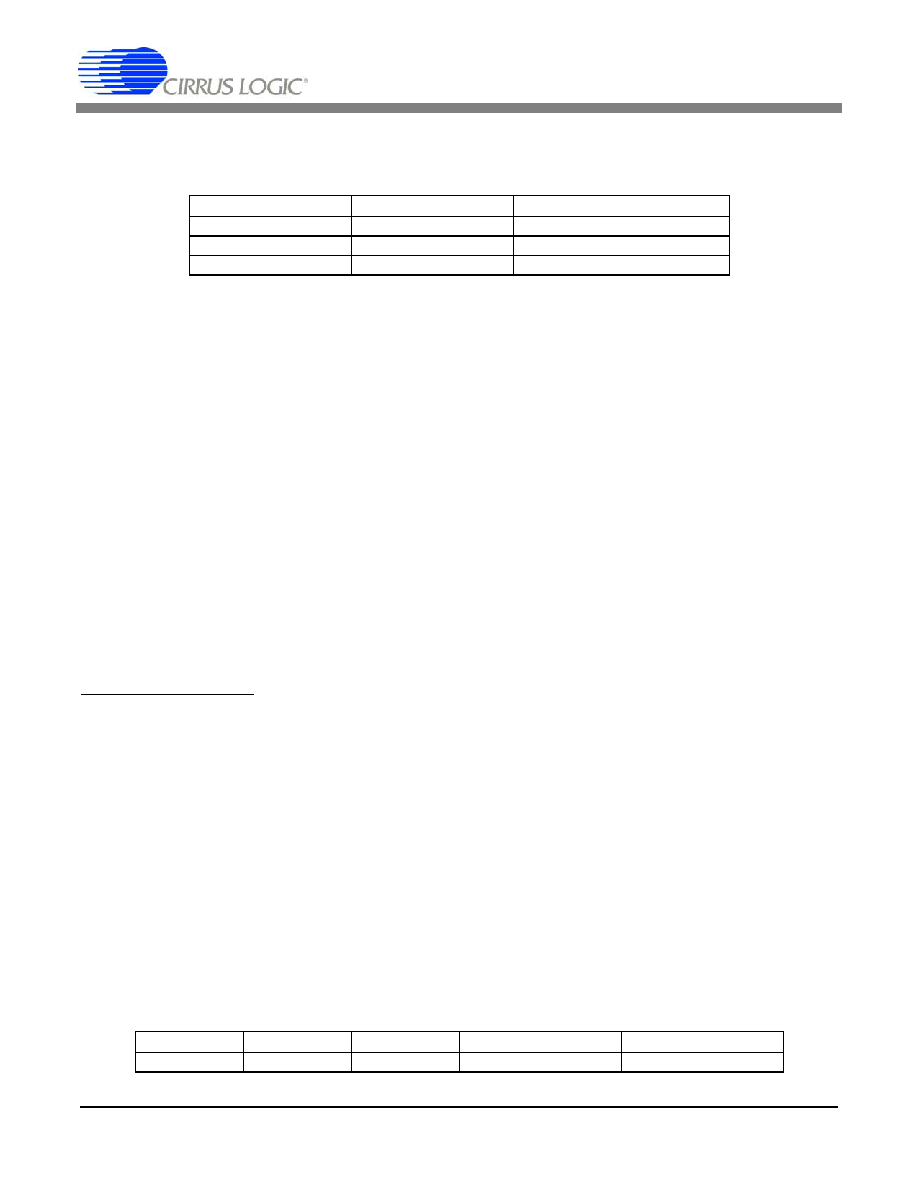

Speed

10BT_SER pin

Nominal frequency

100 Mb/s

n/a

25 MHz

10 Mb/s

low (parallel)

2.5 MHz

10 Mb/s

high (serial)

10 MHz

AN1 pin

AN0 pin

Speed

Forced/Auto

Full/Half Duplex

0

M

10 Mb/s

Forced

Half

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY8CLED04DOCD1-56LTXI | IC POWERPSOC DEBUG 4CH 1A 56VQFN |

| CYG2217 | IC MOD PHONE LINE WIRE 1.07" PCB |

| DAC312ER | IC DAC 12BIT MULT HS 20-CDIP |

| DAC8143FPZ | IC DAC 12BIT DAISYCHAIN 16DIP |

| DAC8228FSZ | IC DAC 8BIT DUAL V-OUT 20SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS8952-IQZR | 功能描述:以太網(wǎng) IC IC 100BASE-TX and 10BASE-T Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| CS8952T | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-CQ | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-IQ | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-IQR | 制造商:Cirrus Logic 功能描述:ETHERNET TXRX SGL CHIP 1-PORT 5V 10MBPS/100MBPS 100TQFP - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。