- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376976 > DS3160 Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號(hào): | DS3160 |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 78/107頁 |

| 文件大?。?/td> | 592K |

| 代理商: | DS3160 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁當(dāng)前第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁

DS3160

78 of 107

CRC, abort sequence detected, packet too small, not an integral number of octets, or an overrun occurred).

This bit is cleared when read and is not set again until another message end is detected. The setting of this

bit can cause a hardware interrupt to occur if the RPE bit in the interrupt mask for the HSR (IHSR)

register is set to a 1 and the HDLC bit in the interrupt mask for the MSR (IMSR) register is set to a 1. The

interrupt is allowed to clear when this bit is read.

Bit 7/Transmit FIFO Underrun (TUDR).

This latched read-only event-status bit is set to a 1 each time

the transmit FIFO underruns and an abort is automatically sent. This bit is cleared when read and is not

set again until another underrun occurs (i.e., the FIFO has been written to and then allowed to empty

again). The setting of this bit can cause a hardware interrupt to occur if the TUDR bit in the interrupt

mask for the HSR (IHSR) register is set to a 1 and the HDLC bit in the interrupt mask for the MSR

(IMSR) register is set to a 1. The interrupt is allowed to clear when this bit is read.

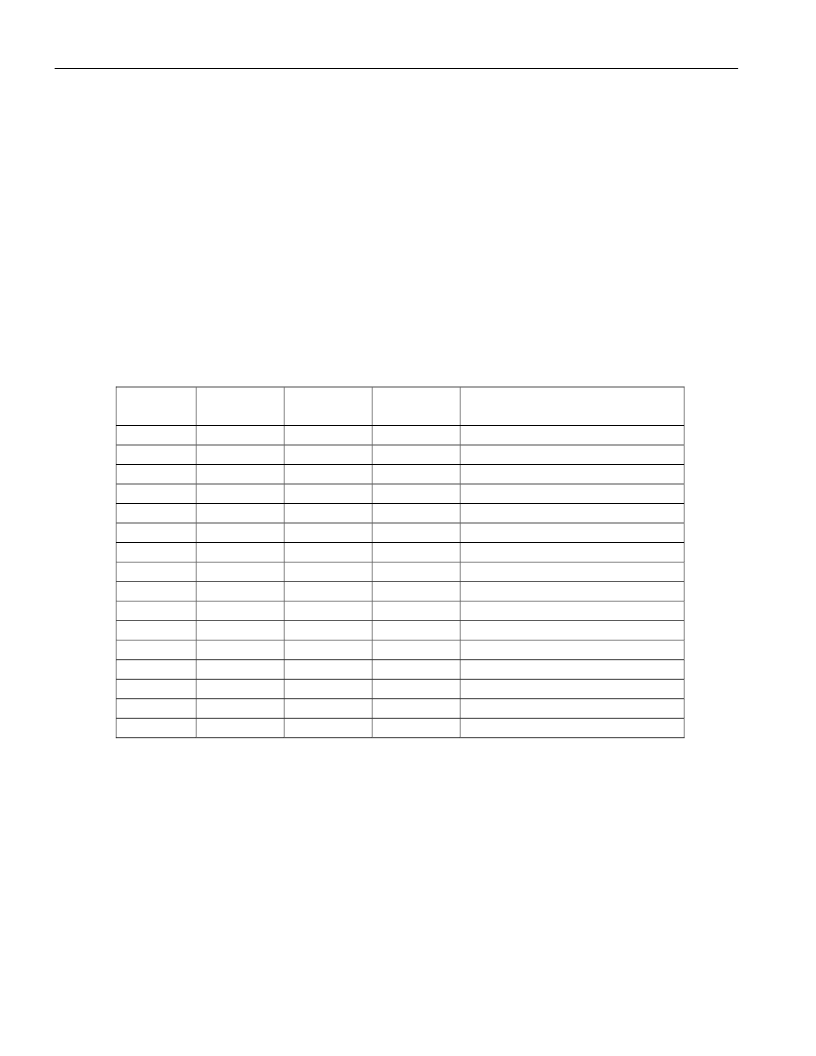

Bit 8 to 11/Transmit FIFO Level Bits 0 to 3 (TFL0 to TFL3).

These read-only real-time status bits

indicate the current depth of the transmit FIFO with a 16-byte resolution. These status bits cannot cause a

hardware interrupt.

TFL3

TFL2

TFL1

TFL0

TRANSMIT FIFO LEVEL

(BYTES)

Empty to 15

16 to 31

32 to 47

48 to 63

64 to 79

80 to 95

96 to 111

112 to 127

128 to 143

144 to 159

160 to 175

176 to 191

192 to 207

208 to 223

224 to 239

240 to 256

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Bit 12/Transmit FIFO Empty (TEMPTY).

This read-only real-time status bit is set to a 1 when the

transmit FIFO is empty. It is cleared when the transmit FIFO contains one or more bytes. This status bit

cannot cause a hardware interrupt.

Bit 13/Receive FIFO Overrun (ROVR).

This latched read-only event-status bit is set to a 1 each time

the receive FIFO overruns. This bit is cleared when read and is not set again until another overrun occurs

(i.e., the FIFO has been read from and then allowed to fill up again). The setting of this bit can cause a

hardware interrupt to occur if the ROVR bit in the interrupt mask for the HSR (IHSR) register is set to a 1

and the HDLC bit in the interrupt mask for the MSR (IMSR) register is set to a 1. The interrupt is allowed

to clear when this bit is read.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS3171 | Single/Dual/Triple/Quad DS3/E3 Single-Chip Transceivers |

| DS3171N | Single/Dual/Triple/Quad DS3/E3 Single-Chip Transceivers |

| DS3172 | Single/Dual/Triple/Quad DS3/E3 Single-Chip Transceivers |

| DS3172N | Single/Dual/Triple/Quad DS3/E3 Single-Chip Transceivers |

| DS3173 | Single/Dual/Triple/Quad DS3/E3 Single-Chip Transceivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3161 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Sgl ATM/Packet PHYs for DS3/E3/STS-1 RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS31612 | 制造商:Maxim Integrated Products 功能描述:12 PORT ATM/PHY 676-TEPBGA - Trays |

| DS31612N | 制造商:Maxim Integrated Products 功能描述:12 PORT ATM/PHY 676-TEPBGA IND - Trays |

| DS3161N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Sgl ATM/Packet PHYs for DS3/E3/STS-1 RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3162 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Dual ATM/Packet PHYs for DS3/E3/STS-1 RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。