- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T8100 H.100/H.110 Interface and Time-Slot Interchanger PDF資料下載

參數(shù)資料

| 型號(hào): | T8100 |

| 英文描述: | H.100/H.110 Interface and Time-Slot Interchanger |

| 中文描述: | H.100/H.110接口和時(shí)隙交換器 |

| 文件頁數(shù): | 9/92頁 |

| 文件大?。?/td> | 1450K |

| 代理商: | T8100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

Lucent Technologies Inc.

7

Preliminary Data Sheet

August 1998

H.100/H.110 Interface and Time-Slot Interchanger

Ambassador T8100

1 Product Overview

(continued)

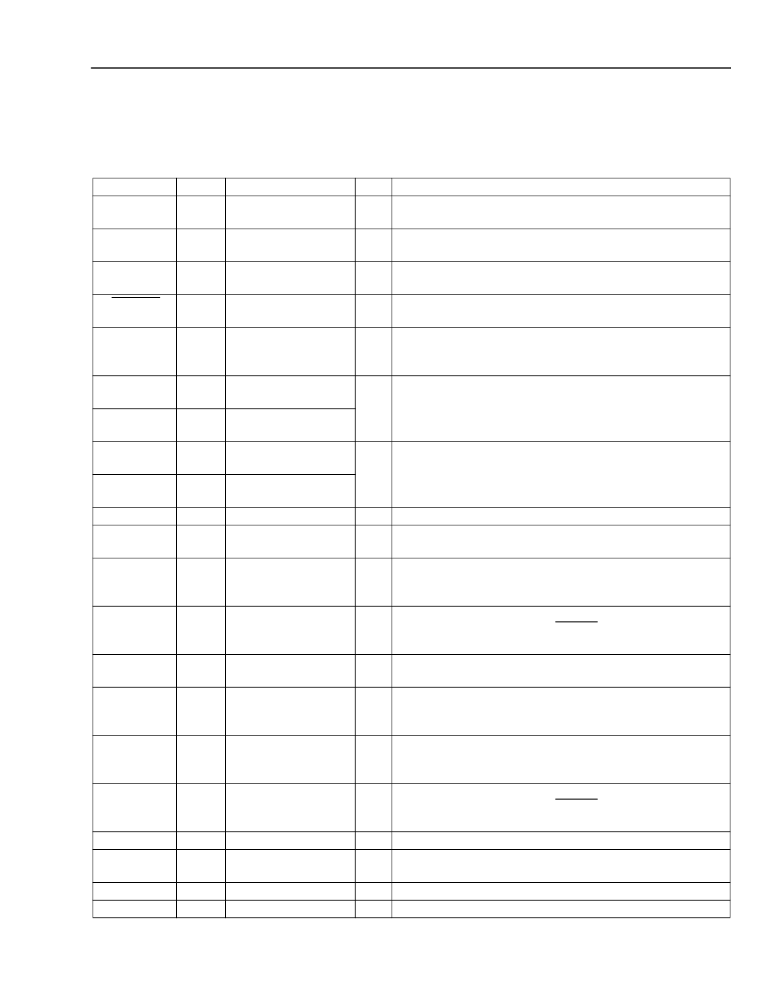

1.3 Pin Information

(continued)

Table 1. Pin Descriptions: Clocking and Framing Pins

(continued)

Symbol

/C4

Pin

104

Ball

U16

Type

I/O

Name/Description

MVIP4.096 MHz Clock.

8 mA drive, Schmitt in, 50 k

internal pull-up.

MVIP2.048 MHz Clock.

8 mA drive, Schmitt in, 50 k

internal pull-up.

SC-Bus 2/4/8 MHz Clock.

24 mA drive, Schmitt in, 50 k

internal pull-up.

SC-Bus Inverted 4/8 MHz Clock (Active-Low).

24 mA

drive, Schmitt in, 50 k

internal pull-up.

Local Selected Clocks.

1.024 MHz, 2.048 MHz,

4.096 MHz, 8.192 MHz, 16.384 MHz, frame (8 kHz), or sec-

ondary (NETREF). 8 mA drive, 3-state.

Frame Group A.

8 mA drive, 3-state.

C2

106

T17

I/O

SCLK

110

R17

I/O

SCLKX2

108

P15

I/O

L_SC[3:0]

36—33

M3, N1, M2, M1

O

FGA[5:0]

94—99 R12, T13, U14, P12,

R13, T14

87—92 T11, P11, R11, U12,

T12, U13

80—85

U9, R9, U10, T10,

R10, U11

73—78

U6, T7, R8, U7, T8,

O

FGA[11:6]

FGB[5:0]

O

Frame Group B.

8 mA drive, 3-state.

FGB[11:6]

U8

P5

U1

PRIREFOUT

PLL1V

DD

58

53

O

—

Output from Primary Clock Selector/Divider.

8 mA drive.

PLL #1 VCO Power.

This pin must be connected to power,

even if PLL #1 is not used.

PLL #1 VCO Ground.

This pin must be connected to

ground, even if PLL #1 is not used.

PLL1GND

51

No ball for this

signal, internally

connected.

T3

—

EN1

55

I

PLL #1 Enable.

Requires cap to V

SS

to form power-on

reset, or may be driven with RESET line. 50 k

internal

pull-up.

PLL #1 Rate Multiplier.

Can be 2.048 MHz or 4.096 MHz.

50 k

internal pull-up.

PLL #2 VCO Power.

This pin must be connected to power

if PLL #2 is not used and 3MHZIN is used. Can be left float-

ing only if both PLL #2 and 3MHZIN are not used.

PLL #2 VCO Ground.

This pin must be connected to

ground if PLL #2 is not used and 3MHZIN is used. Can be

left floating only if both PLL #2 and 3MHZIN are not used.

PLL #2 Enable.

Requires cap to V

SS

to form power-on

reset, or may be driven with RESET line. 50 k

internal

pull-up.

PLL #2 Rate Multiplier.

Input, 50 k

internal pull-up.

16.384 MHz Crystal Connection or External Clock

Input.

16.384 MHz Crystal, Feedback Connection.

Selected output to drive framers. 8 mA drive, 3-state.

4MHZIN

54

U2

I

PLL2V

DD

208

A2

—

PLL2GND

206

No ball for this

signal, internally

connected.

C2

—

EN2

3

I

3MHZIN

XTALIN

1

A1

R2

I

I

47

XTALOUT

TCLKOUT

48

203

T1

C4

O

O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8110 | Version History |

| T8301 | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

| T8302 | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| T8502 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8503 | T8502 and T8503 Dual PCM Codecs with Filters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8-1003 | 制造商:Hakko 功能描述:HAKKO TIP T8-1003 制造商:HAKKO Corporation 功能描述:HAKKO TIP T8-1003 |

| T8-1004 | 制造商:Hakko 功能描述:HAKKO TIP T8-1004 制造商:HAKKO Corporation 功能描述:HAKKO TIP T8-1004 |

| T8-1005 | 制造商:Hakko 功能描述:HAKKO TIP T8-1005 制造商:HAKKO Corporation 功能描述:HAKKO TIP T8-1005 |

| T8-1007 | 制造商:Hakko 功能描述:HAKKO TIP T8-1007 制造商:HAKKO Corporation 功能描述:HAKKO TIP T8-1007 |

| T8100A | 制造商:AGERE 制造商全稱:AGERE 功能描述:H.100/H.110 Interface and Time-Slot Interchangers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。