- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T8301 T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP PDF資料下載

參數(shù)資料

| 型號(hào): | T8301 |

| 英文描述: | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

| 中文描述: | T8301因特網(wǎng)協(xié)議電話熱線電話在一個(gè)芯片⑩DSP的IP解決方案 |

| 文件頁(yè)數(shù): | 54/190頁(yè) |

| 文件大?。?/td> | 1535K |

| 代理商: | T8301 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)當(dāng)前第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)

Data Sheet

March 2000

DSP1627 Digital Signal Processor

18

Lucent Technologies Inc.

4 Hardware Architecture

(continued)

Data Memory Mapping

On the data memory side (see Table 6), the six 1K

banks of dual-port RAM are located starting at address

0. Addresses from 0x4000 to 0x40FF reference a 256-

word memory-mapped I/O segment (IO). Addresses

from 0x4100 to 0x7FFF reference the low external data

RAM segment (ERAMLO). Addresses above 0x8000

reference high external data RAM (ERAMHI).

Wait-States

The number of wait-states (from 0 to 15) used when ac-

cessing each of the four external memory segments

(ERAMLO, IO, ERAMHI, and EROM) is programmable

in the mwait register (see Table 36). When the program

references memory in one of the four external seg-

ments, the internal multiplexer is automatically switched

to the appropriate set of internal buses, and the associ-

ated external enable of ERAMLO, IO, ERAMHI, or

EROM is issued. The external memory cycle is auto-

matically stretched by the number of wait-states config-

ured in the appropriate field of the mwait register.

4.5 External Memory Interface (EMI)

The external memory interface supports read/write op-

erations from instruction/coefficient memory, data

memory, and memory-mapped I/O devices. The

DSP1627 provides a 16-bit external address bus,

AB[15:0], and a 16-bit external data bus, DB[15:0].

These buses are multiplexed between the internal bus-

es for the instruction/coefficient memory and the data

memory. Four external memory segment enables,

ERAMLO, IO, ERAMHI, and EROM, select the external

memory segment to be addressed.

If a data memory location with an address between

0x4100 and 0x7FFF is addressed, ERAMLO is asserted

low.

If one of the 256 external data memory locations, with

an address greater than or equal to 0x4000, and less

than or equal to 0x40FF, is addressed, IO is asserted

low. IO is intended for memory-mapped I/O.

If a data memory location with an address greater than

or equal to 0x8000 is addressed, ERAMHI is asserted

low. When the external instruction/coefficient memory is

addressed, EROM is asserted low.

The flexibility provided by the programmable options of

the external memory interface (see Table 36, mwait

Register and Table 38, ioc Register) allows the

DSP1627 to interface gluelessly with a variety of com-

mercial memory chips.

Each of the four external memory segments, ERAMLO,

IO, ERAMHI, and EROM, has a number of wait-states

that is programmable (from 0 to 15) by writing to the

mwait register. When the program references memory

in one of the four external segments, the internal multi-

plexer is automatically switched to the appropriate set of

internal buses, and the associated external enable of

ERAMLO, IO, ERAMHI, or EROM is issued. The exter-

nal memory cycle is automatically stretched by the num-

ber of wait-states in the appropriate field of the mwait

register.

When writing to external memory, the RWN pin goes

low for the external cycle. The external data bus,

DB[15:0], is driven by the DSP1627 starting halfway

through the cycle. The data driven on the external data

bus is automatically held after the cycle unless an exter-

nal read cycle immediately follows.

The DSP1627 has one external address bus and one

external data bus for both memory spaces. Since some

instructions provide the capability of simultaneous ac-

cess to both X space and Y space, some provision must

be made to avoid collisions for external accesses. The

DSP1627 has a sequencer that does the external X ac-

cess first, and then the external Y access, transparently

to the programmer. Wait-states are maintained as

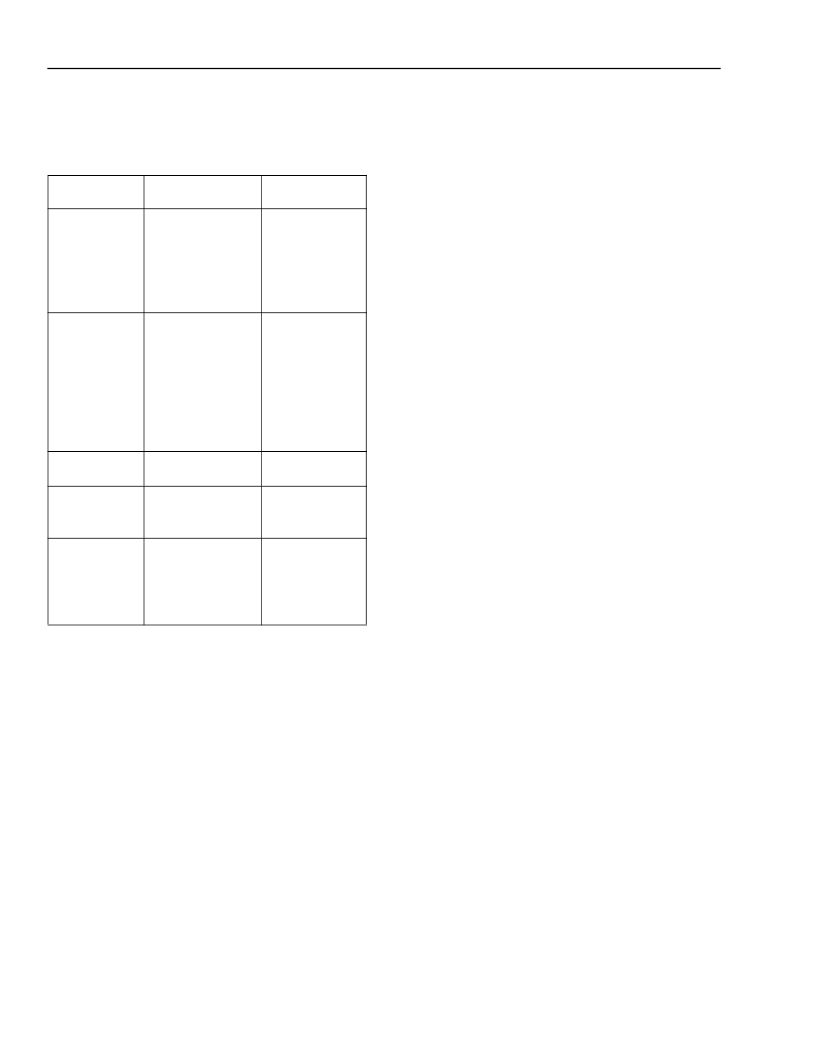

Table 6. Data Memory Map (Not to Scale)

Decimal

Address

0

Address in

r0, r1, r2, r3

0x0000

Segment

DPRAM[1:6]

6K

0x1800

Reserved

(10K)

16K

0x4000

IO

16,640

0x4100

ERAMLO

32K

0x8000

ERAMHI

64K – 1

0xFFFF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8302 | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| T8502 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8503 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8531A | T8531A/8532 Multichannel Programmable Codec Chip Set |

| T8531 | T8502 and T8503 Dual PCM Codecs with Filters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8301AX | 制造商:MOLEX 制造商全稱:Molex Electronics Ltd. 功能描述:Terminator Die |

| T8301BX | 制造商:MOLEX 制造商全稱:Molex Electronics Ltd. 功能描述:Terminator Die |

| T8301DX | 制造商:MOLEX 制造商全稱:Molex Electronics Ltd. 功能描述:Terminator Die |

| T8302 | 制造商:AGERE 制造商全稱:AGERE 功能描述:T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| T8302A | 制造商:MOLEX 制造商全稱:Molex Electronics Ltd. 功能描述:Terminator Die |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。