- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371179 > T8301 T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP PDF資料下載

參數(shù)資料

| 型號(hào): | T8301 |

| 英文描述: | T8301 Internet Protocol Telephone Phone-On-A-Chip⑩ IP Solution DSP |

| 中文描述: | T8301因特網(wǎng)協(xié)議電話熱線電話在一個(gè)芯片⑩DSP的IP解決方案 |

| 文件頁(yè)數(shù): | 58/190頁(yè) |

| 文件大小: | 1535K |

| 代理商: | T8301 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)當(dāng)前第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)

Data Sheet

March 2000

DSP1627 Digital Signal Processor

22

Lucent Technologies Inc.

4 Hardware Architecture

(continued)

4.8 Parallel Host Interface (PHIF)

The DSP1627 has an 8-bit parallel host interface for rap-

id transfer of data with external devices. This parallel port

is passive (data strobes provided by an external device)

and supports either Motorola or Intel microcontroller pro-

tocols. The PHIF also provides for 8-bit or 16-bit data

transfers. As a flexible host interface, it requires little or

no glue logic to interface to other devices (e.g., microcon-

trollers, microprocessors, or another DSP).

The data path of the PHIF consists of a 16-bit input buff-

er,

pdx0

(in), and a 16-bit output buffer,

pdx0

(out). Two

output pins, parallel input buffer full (PIBF) and parallel

output buffer empty (POBE), indicate the state of the

buffers. In addition, there are two registers used to con-

trol and monitor the PHIF's operation: the parallel host in-

terface control register (

phifc

, see Table 28), and the

PHIF status register (PSTAT, see Table 8). The PSTAT

register, which reflects the state of the PIBF and POBE

flags, can only be read by an external device when the

PSTAT input pin is asserted. The

phifc

register defines

the programmable options for this port.

The function of the pins, PIDS and PODS, is programma-

ble to support both the Inteland Motorolaprotocols. The

pin, PCSN, is an input that, when low, enables PIDS and

PODS (or PRWN and PDS, depending on the protocol

used). While PCSN is high, the DSP1627 ignores any ac-

tivity on PIDS and/or PODS. If a DSP1627 is intended to

be continuously accessed through the PHIF port, PCSN

should be grounded. If PCSN is low and their respective

bits in the

inc

register are set, the assertion of PIDS and

PODS by an external device causes the DSP1627 de-

vice to recognize an interrupt.

Programmability

The parallel host interface can be programmed for 8-bit

or 16-bit data transfers using bit 0, PMODE, of the

phifc

register. Setting PMODE selects 16-bit transfer mode.

An input pin controlled by the host, PBSEL, determines

an access of either the high or low bytes. The assertion

level of the PBSEL input pin is configurable in software

using bit 3 of the

phifc

register, PBSELF. Table 7 sum-

marizes the port's functionality as controlled by the

PSTAT and PBSEL pins and the PBSELF and PMODE

fields.

For 16-bit transfers, if PBSELF is zero, the PIBF and

POBE flags are set after the high byte is transferred. If

PBSELF is one, the flags are set after the low byte is

transferred. In 8-bit mode, only the low byte is accessed,

and every completion of an input or output access sets

PIBF or POBE.

Bit 1 of the

phifc

register, PSTROBE, configures the port

to operate either with an Intelprotocol where only the

chip select (PCSN) and either of the data strobes (PIDS

or PODS) are needed to make an access, or with a Mo-

torolaprotocol where the chip select (PCSN), a data

strobe (PDS), and a read/write strobe (PRWN) are need-

ed. PIDS and PODS are negative assertion data strobes

while the assertion level of PDS is programmable

through bit 2, PSTRB, of the

phifc

register.

Finally, the assertion level of the output pins, PIBF and

POBE, is controlled through bit 4, PFLAG. When PFLAG

is set low, PIBF and POBE output pins have positive as-

sertion levels. By setting bit 5, PFLAGSEL, the logical

OR of PIBF and POBE flags (positive assertion) is seen

at the output pin PIBF. By setting bit 7 in

phifc

, PSOBEF,

the polarity of the POBE flag in the status register,

PSTAT, can be changed. PSOBEF has no effect on the

POBE pin.

Pin Multiplexing

Please refer to Pin Multiplexing in Section 4.1 for a de-

scription of BIO, PHIF, VEC[3:0], and SIO2 pins.

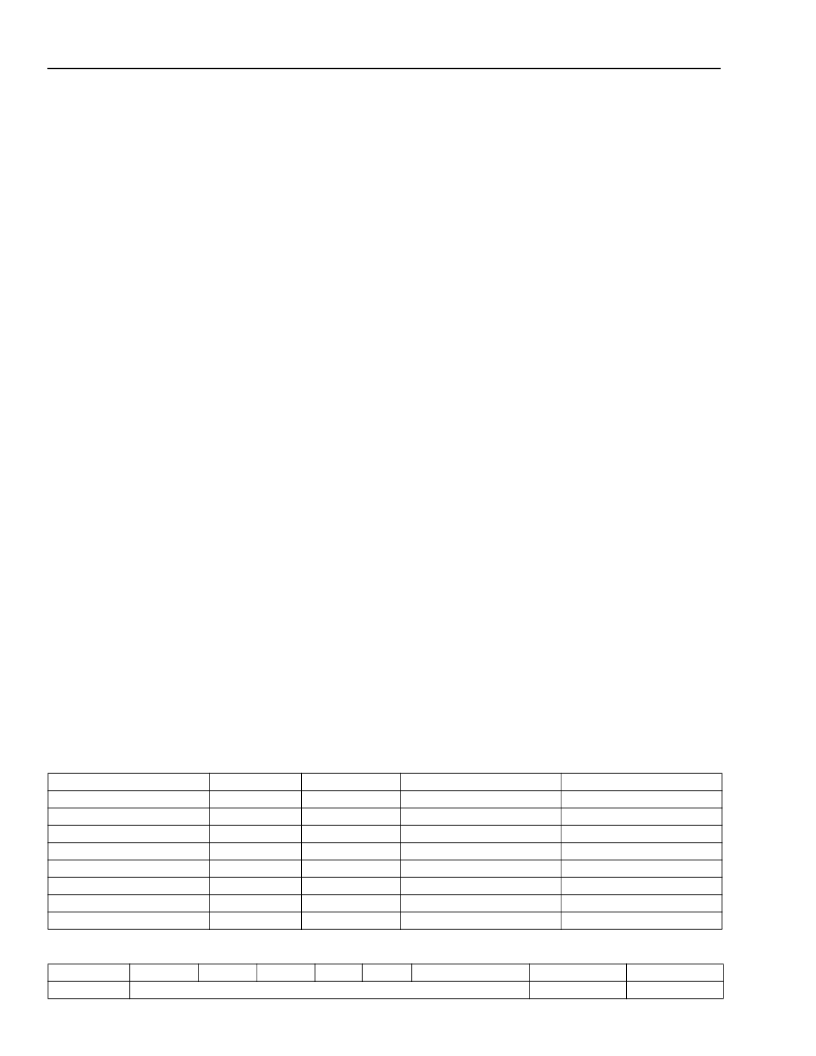

Table 7. PHIF Function (8-bit and 16-bit Modes)

PMODE Field

0 (8-bit)

0

0

0

1 (16-bit)

1

1

1

PSTAT Pin

0

0

1

1

0

0

1

1

PBSEL Pin

0

1

0

1

0

1

0

1

PBSELF Field = 0

pdx0 low byte

reserved

PSTAT

reserved

pdx0 low byte

pdx0 high byte

PSTAT

reserved

PBSELF Field = 1

reserved

pdx0 low byte

reserved

PSTAT

pdx0 high byte

pdx0 low byte

reserved

PSTAT

Table 8. pstat Register as Seen on PB[7:0]

Bit

Field

7

6

5

4

3

2

1

0

RESERVED

PIBF

POBE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T8302 | T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| T8502 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8503 | T8502 and T8503 Dual PCM Codecs with Filters |

| T8531A | T8531A/8532 Multichannel Programmable Codec Chip Set |

| T8531 | T8502 and T8503 Dual PCM Codecs with Filters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T8301AX | 制造商:MOLEX 制造商全稱(chēng):Molex Electronics Ltd. 功能描述:Terminator Die |

| T8301BX | 制造商:MOLEX 制造商全稱(chēng):Molex Electronics Ltd. 功能描述:Terminator Die |

| T8301DX | 制造商:MOLEX 制造商全稱(chēng):Molex Electronics Ltd. 功能描述:Terminator Die |

| T8302 | 制造商:AGERE 制造商全稱(chēng):AGERE 功能描述:T8302 Internet Protocol Telephone Advanced RISC Machine (ARM) Ethernet QoS Using IEEE 802.1q |

| T8302A | 制造商:MOLEX 制造商全稱(chēng):Molex Electronics Ltd. 功能描述:Terminator Die |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。