- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359438 > VT6516 (Electronic Theatre Controls, Inc.) 16/12 PORT 10/1000 ASE T/TX PDF資料下載

參數(shù)資料

| 型號: | VT6516 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 16/12 PORT 10/1000 ASE T/TX |

| 中文描述: | 16/12港口10/1000日月光噸/德克薩斯州 |

| 文件頁數(shù): | 44/73頁 |

| 文件大?。?/td> | 440K |

| 代理商: | VT6516 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

VIA Technologies, Inc.

Preliminary VT6516 Datarsheet

-

44-

5000H

MAC & I/O Control Module of Port

11

MAC & I/O Control Module of Port

12

MAC & I/O Control Module of Port

13

MAC & I/O Control Module of Port

14

MAC & I/O Control Module of Port

15

CPU IO Control Module

CPU packet read byte count register bits

[7:0]

CPU packet read byte count register bits

[10:8]

CPU packet read status register

as same as Port 0

5400H

as same as Port 0

5800H

as same as Port 0

5C00H

as same as Port 0

6000H

as same as Port 0

6400H

00H

PKT_BYTE_C

NT

PKT_BYTE_C

NT

RD_PKT_STA

TUS

PKT_SRC_PO

RT

CPUIO_CFG

[7:0] 0

R/O

01H

[10:8

]

[1:0] 0

0

R/O

02H

R/O

03H

Packet source port ID

[3:0] 0

R/O

04H

CPU IO port configuration register

[1:0] 0

R/

W

R/O

10H

CPU packet write status register

WR_PKT_STA

TUS

[2:0] 0

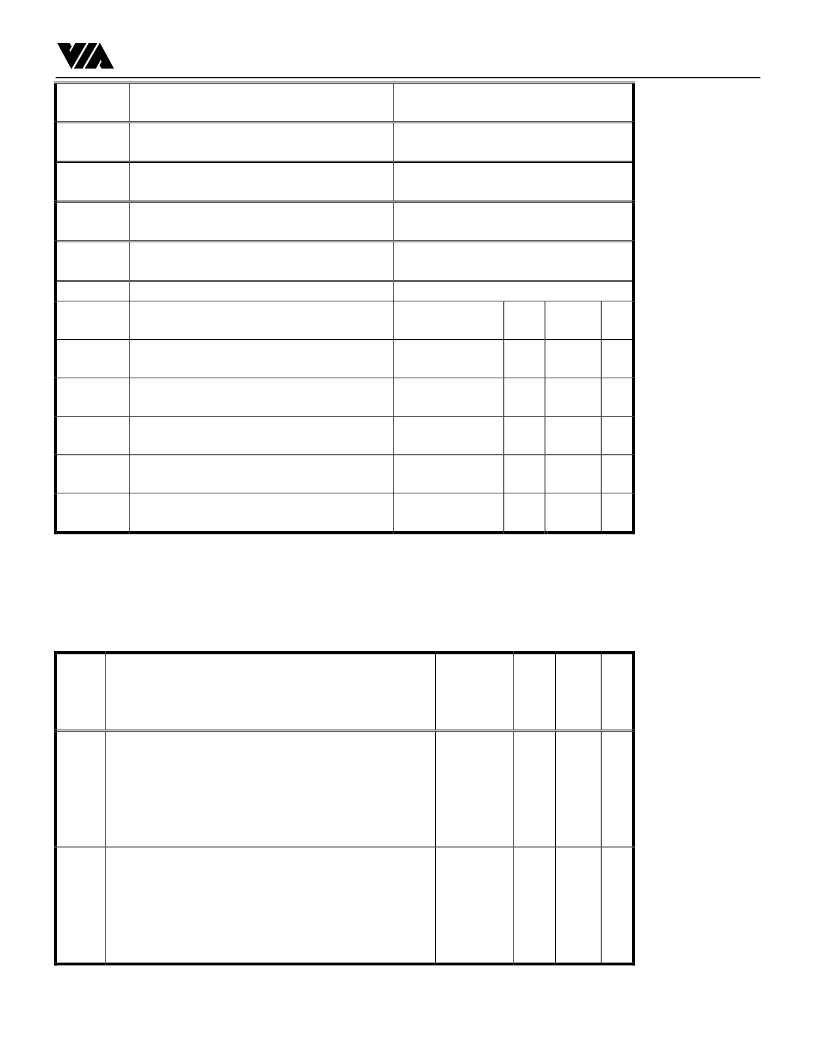

4. D

ETAIL OF

S

WITCH

R

EGISTER

4.1 Registers of SDRAM Control Module

* Base Address: 0000H

Addres

s

(offset

)

00H

SDRAM TYPE:

0: 16Mbit SDRAM chip (default)

1: 64Mbit

Function

Register

Name

Bits

Defau

lt

Value

R/

W

This register has to be specified before initialization of the buffer

control because the Bank 1 free buffer pointer should have initial

value 130 for 16Mbit SDRAM, or, initial value 131 for 64Mbit

SDRAM.

CAS Latency for read operation:

2’b00: latency 1

2’b01: latency 2

2’b10: latency 3 (default)

SDRAMTYPE [0]

0

R/W

01H

This latency specifies the required delay between the CAS cycle and

the first read cycle. Note that the CAS latency has to be specified

before using RSDM in SDRAM initialization.

CL

[1:0]

2

R/W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VT70A144 | |

| VT74A451 | |

| VT74A901 | |

| VT77A142 | |

| VT77A202 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VT-6-6 | 制造商:Panduit Corp 功能描述:BOLT TERM 70MM 57MM - Bulk 制造商:Panduit Corp 功能描述:Bolt Terminal 70mm 57mm |

| VT6J1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:1.2V Drive Pch + Pch MOSFET |

| VT6K1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:1.2V Drive Nch + Nch MOSFET |

| VT6K1T2CR | 制造商:ROHM Semiconductor 功能描述: |

| VT6M1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:1.2V Drive Nch + Pch MOSFET |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。