- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359438 > VT6516 (Electronic Theatre Controls, Inc.) 16/12 PORT 10/1000 ASE T/TX PDF資料下載

參數(shù)資料

| 型號(hào): | VT6516 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 16/12 PORT 10/1000 ASE T/TX |

| 中文描述: | 16/12港口10/1000日月光噸/德克薩斯州 |

| 文件頁(yè)數(shù): | 54/73頁(yè) |

| 文件大小: | 440K |

| 代理商: | VT6516 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)當(dāng)前第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)

VIA Technologies, Inc.

Preliminary VT6516 Datarsheet

-

54-

Addres

s

(offset

)

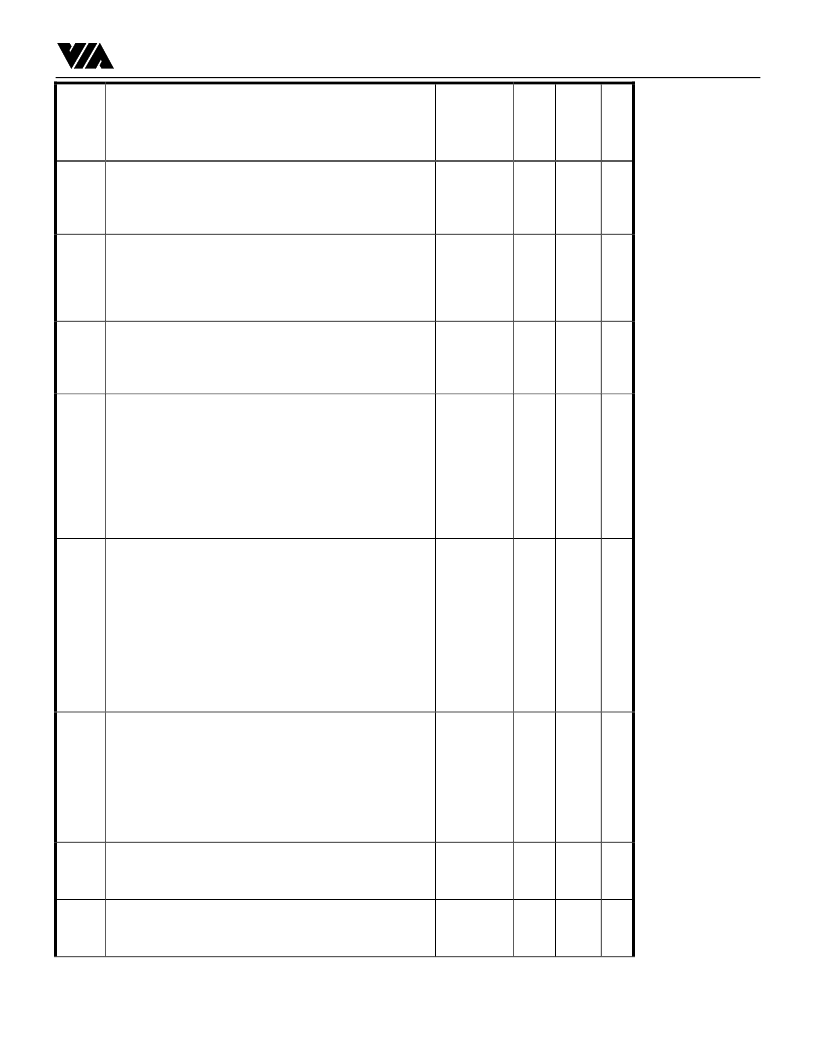

00H

Function

Register

Name

Bits

Defau

lt

Value

R/

W

PHY ID

This is used to specify which PHY device is the objective of the

following MII commands. There are maximum 16 RMII PHY

devices.

PHY register address

PHYID

[3:0] 0

W/

O

01H

In each PHY device, there are maximum 32 MII management

registers accessible by the CPU. The PHY_REG_ADDR register is

used to specify which one is the objective of the following access

command.

PHY data register

PHY_REG

_ADDR

[4:0] 0

W/

O

02-

03H

Each PHY management register is 16 bits. Every data access to a

PHY management register is in unit of 16 bits, stored in this

register.

PHY command register

1: read

0: write

PHYDAT

A

[15:0

]

R/

W

04H

Write 0 to this register will cause a write operation to the PHY

management register (specified by the PHY_REG_ADDR) of the

PHY device (specified by the PHYID). Write 1 to this register will

cause a read operation. A read or write operation takes about 0.4 ms

so that the CPU has to read the PHYSTS register periodically to

check if the issued command is complete.

PHY status register

2’b00: idle

2’b01: busy

2’b10: complete

PHYCMD [0]

W/

O

05H

This register indicates the status of the PHY control module.

Initially, the PHY control module is in the idle status. While a read

or write command is issued by writing 1/0 to the PHYCMD register,

PHYSTS becomes “busy” immediately, and goes into the

“complete” status as this operation finishes. Then, a following “read

status” command will cause it back to the “idle” status, or a

following read/write command will cause it into the “busy” status.

PORT0 PHY Device Address

PHYSTS

[1:0] 0

R/O

10H

The pair of 5-bit PHY device address and 5-bit register address

forms a unique access address to a PHY device’s register. Each PHY

device has a unique device address that is identified by the PHYID.

In the system initialization, the CPU should write PHY device

addresses, corresponding to every PHY devices, to registers

PORT[0..15]_PHY_ADDR, that may be recorded in the EEPROM

or code ROM.

PORT1 PHY Device Address

PORT0_P

HY_ADD

R

[4:0] 0

R/

W

11H

PORT1_P

HY_ADD

R

PORT2_P

HY_ADD

R

[4:0] 0

R/

W

12H

PORT2 PHY Device Address

[4:0] 0

R/

W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VT70A144 | |

| VT74A451 | |

| VT74A901 | |

| VT77A142 | |

| VT77A202 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VT-6-6 | 制造商:Panduit Corp 功能描述:BOLT TERM 70MM 57MM - Bulk 制造商:Panduit Corp 功能描述:Bolt Terminal 70mm 57mm |

| VT6J1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:1.2V Drive Pch + Pch MOSFET |

| VT6K1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:1.2V Drive Nch + Nch MOSFET |

| VT6K1T2CR | 制造商:ROHM Semiconductor 功能描述: |

| VT6M1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:1.2V Drive Nch + Pch MOSFET |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。