- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C974 (Advanced Micro Devices, Inc.) PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C974 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| 中文描述: | PCnetTM -的SCSI結(jié)合以太網(wǎng)和SCSI控制器PCI系統(tǒng) |

| 文件頁數(shù): | 144/153頁 |

| 文件大小: | 838K |

| 代理商: | AM79C974 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁當(dāng)前第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

AMD

A M E N D M E N T

10

Am79C974

Bus Master DMA Transfers

There are four primary types of DMA transfers. The

Am79C974 controller uses non-burst as well as burst

cycles for read and write access to the main memory.

Basic Non-Burst Read Cycles

All Am79C974 controller non-burst read accesses are of

the PCI command type Memory Read (type 6). Note that

during all non-burst read operations, the Am79C974

controller will always activate all byte enables, even

though some byte lanes may not contain valid data as

indicated by a buffer pointer value. In such instances,

the Am79C974 controller will internally discard un-

needed bytes.

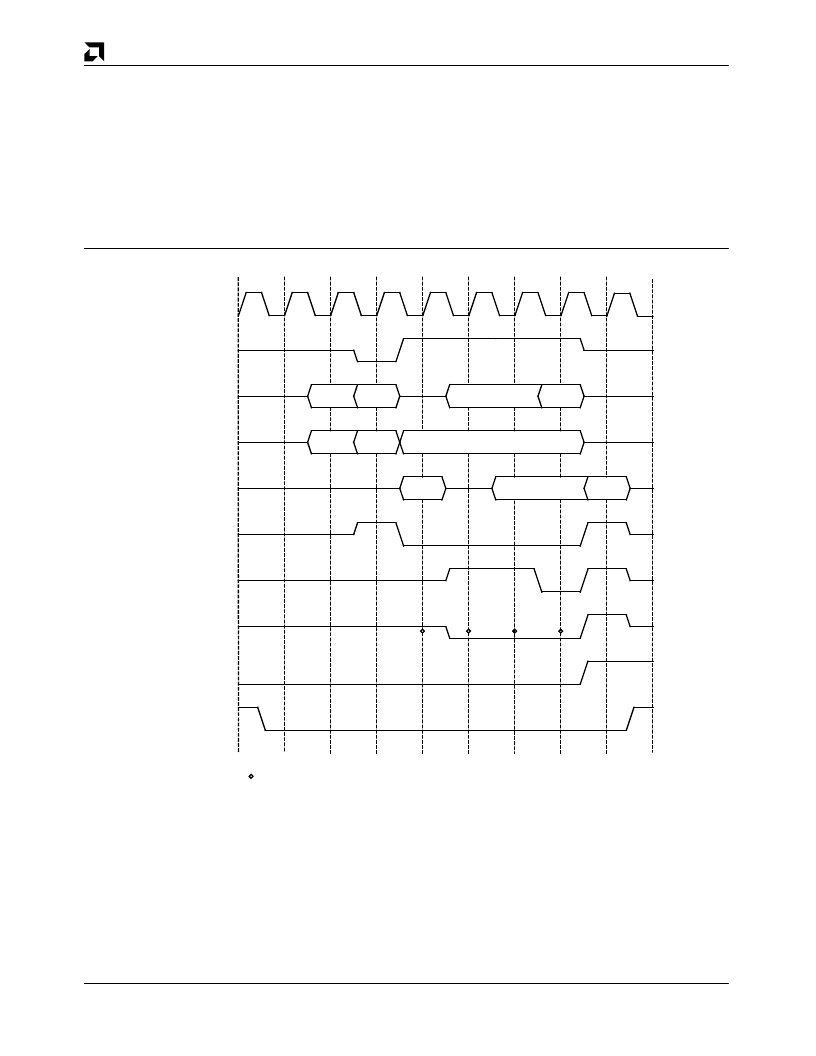

Figure 6 shows a typical non-burst read access. The

Am79C974 controller asserts

IRDY

at clock 5 immedi-

ately after the address phase and starts sampling

DEVSEL

. The target extends the cycle by asserting

DEVSEL

not until clock 6. Additionally, the target inserts

one wait state by asserting its ready (

TRDY

) at clock 8.

18681A/1-10

FRAME

CLK

AD

IRDY

TRDY

C/

BE

DEVSEL

REQ

GNT

1

2

3

4

5

6

7

8

0000

9

PAR

PAR

PAR

DATA

DEVSEL

is sampled by the Am79C974 controller.

ADDR

0110

Figure 6. Non-Burst Read Cycles With Wait States

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C975KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C974KC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C974KC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C974KCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。