- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C974 (Advanced Micro Devices, Inc.) PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems PDF資料下載

參數(shù)資料

| 型號: | AM79C974 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| 中文描述: | PCnetTM -的SCSI結(jié)合以太網(wǎng)和SCSI控制器PCI系統(tǒng) |

| 文件頁數(shù): | 59/153頁 |

| 文件大?。?/td> | 838K |

| 代理商: | AM79C974 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁當(dāng)前第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

P R E L I M I N A R Y

AMD

59

Am79C974

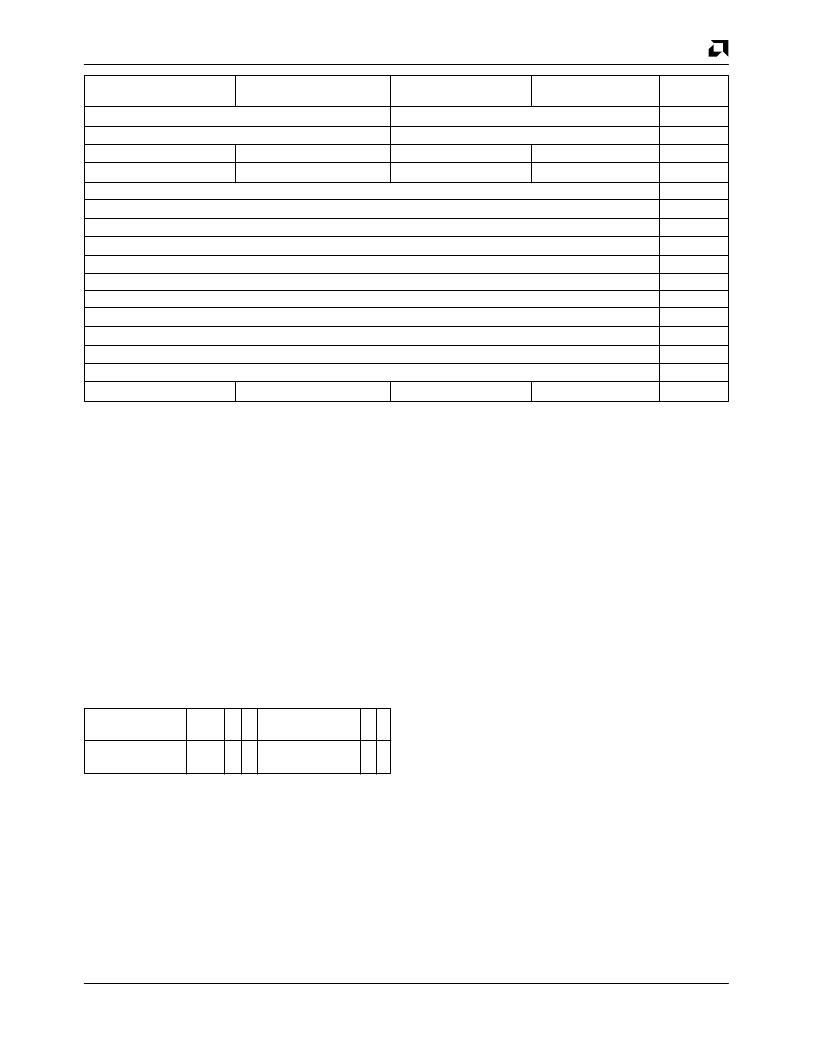

Device ID

Status

Vendor ID

Command

00h

04h

08h

0Ch

10h

14h

18h

1Ch

20h

24h

28h

2Ch

30h

34h

38h

3Ch

Base-Class

Reserved

Sub-Class

Header Type

Programming IF

Latency Timer

Revision ID

Reserved

Base Address

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Interrupt Pin

Interrupt Line

31

24 23

16

15

8

7

0

Offset

The configuration registers are accessible only by PCI

configuration cycles. They can be accessed right after

the Am79C974 controller is powered-on, even if the

read operation of the serial EEPROM is still on-going.

All multi-byte numeric fields follow little endian byte or-

dering. The Command register is the only register

cleared by H_RESET. S_RESET as well as asserting

SLEEP

have no effect on the value of the PCI configura-

tion registers. All write accesses to Reserved locations

have no effect, reads from these locations will return a

data value of ZERO.

When the Am79C974 controller samples its IDSELA or

IDSELB input asserted during a configuration cycle, it

will acknowledge the cycle by asserting its

DEVSEL

out-

put. The content of AD[31:00] during the address phase

of the configuration cycles must meet the format as

shown below:

Don’t

Care

Don’t Care

0 0

DWORD Index

0 0

31

11 10

8 7

6 5

2 1 0

AD[1:0] must both be ZEROs, since the Am79C974

controller is not a bridge device. It only recognizes con-

figuration cycles of Type 0 (as defined by the PCI speci-

fication revision 2.0). AD[7:2] specify the selected

DWORD in the configuration space. AD[7:6] must both

be ZERO, since the Am79C974’s Ethernet controller

does not implement any of the device specific registers

in locations 64 – 255. Since AD[1:0] and AD[7:6] must all

be ZERO, the lower 8 bits of the address for a configura-

tion cycle are equal to the offset of the DWORD counting

from the beginning of the PCI configuration space.

AD[10:8] specify one of eight possible functions of a PCI

device. The Am79C974 controller functions as two sin-

gle function devices, as indicated in the Header Type

registers of both PCI configuration spaces (bit 7,

FUNCT = 0). Therefore, the Am79C974 controller ig-

nores AD[10:8] during the address phase of a configura-

tion cycle. AD[31:11] are typically used to generate the

IDSELA or IDSELB signals. The Am79C974 controller

ignores all upper address bits.

PCI configuration registers can be accessed with 8-bit,

16-bit or 32-bit transfers. The active bytes within a

DWORD are determined by the byte enable signals.

E.G. a read of the Sub-Class register can be performed

by reading from offset 08h with only

BE

2 being active.

I/O Resources

The Am79C974 controller uses two separate blocks of

I/O space, one for the SCSI controller and one for the

Ethernet controller. This section discusses the I/O ad-

dress block used by the Ethernet controller.

PCnet-SCSI’s Ethernet Controller I/O Resource

Mapping

The Am79C974’s Ethernet controller has several I/O re-

sources. These resources use 32 bytes of I/O space

that begin at the Am79C974’s Ethernet controller I/O

base address.

The Ethernet controller allows two modes of slave ac-

cess. Word I/O mode treats all Ethernet controller I/O

Resources as two-byte entities spaced at two-byte ad-

dress intervals. Double Word I/O mode treats all Ether-

net controller I/O Resources as four-byte entities

spaced at four-byte address intervals. The selection of

WIO or DWIO mode is accomplished in any of

severalways:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C975KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C974KC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C974KC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C974KCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。