- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C974 (Advanced Micro Devices, Inc.) PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems PDF資料下載

參數(shù)資料

| 型號: | AM79C974 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| 中文描述: | PCnetTM -的SCSI結(jié)合以太網(wǎng)和SCSI控制器PCI系統(tǒng) |

| 文件頁數(shù): | 83/153頁 |

| 文件大小: | 838K |

| 代理商: | AM79C974 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁當前第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

P R E L I M I N A R Y

AMD

83

Am79C974

continue until the Current Transfer Count Register dec-

rements to zero.

Non-DMA commands do not modify the Current Trans-

fer Count Register and are unaffected by the value in the

Current Transfer Count Register. For non-DMA com-

mands, the number of bytes transmitted depends solely

on the operation in progress.

When non-DMA commands are used, the host com-

puter must use programmed I/O to transfer the data be-

tween the SCSI FIFO and the host memory.

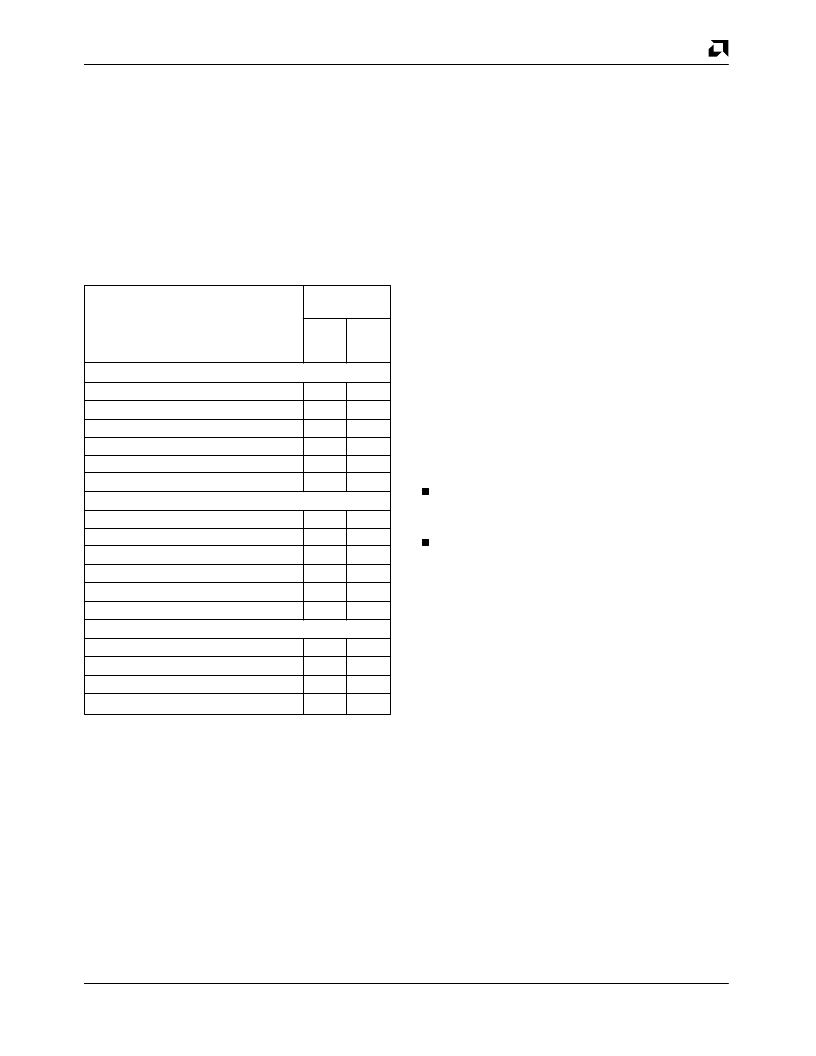

Table 7. Summary of Commands

Initiator Commands

Information Transfer

Initiator Command Complete Steps

Message Accepted

Transfer Pad Bytes

Set

ATN

*

Reset

ATN

*

Idle State Commands

Select without

ATN

Steps

Select with

ATN

Steps

Select with

ATN

and Stop Steps

Enable Selection/Reselection*

Disable Selection/Reselection

Select with

ATN

3 Steps

General Commands

No Operation*

Clear FIFO*

Reset Device*

Reset SCSI Bus**

10

11

12

–

1A

1B

90

91

–

98

–

–

41

42

43

44

45

46

C1

C2

C3

C4

–

C6

00

01

02

03

80

–

–

–

Non-

DMA

Mode

DMA

Mode

Code

(Hex.)

Command

Notes:

* These commands do not generate interrupt.

** An interrupt is generated when SCSI bus reset interrupt

reporting is not disabled (see Control Register1/DISR

bit6).

Command Stacking

The microprocessor may stack commands in the Com-

mand Register ((B)+0Ch) since it functions as a two-

byte deep FIFO. Non-DMA commands may not be

stacked, and commands which transfer data in oppos-

ing directions should not be stacked together; other-

wise, the results are unpredictable.

If DMA commands are queued together, the Start

Transfer Count must be written before the associated

command is loaded into the Command Register. Since

multiple interrupts can occur when commands are

stacked, it is recommended that the ENF bit in Control

Register Two (Bit 6) be set in order to latch the SCSI

phase bits in the SCSI Status Register ((B)+10h) at the

completion of a command. This allows the host to deter-

mine the phase of the interrupting command without

having to consider phase changes that occurred after

the stacked command began execution.

Note

: Command stacking should only be used during

SCSI Data In or Data Out transfers.

Invalid Commands

When an illegal command is written to the Am79C974,

the Invalid Command Bit (Bit 6, Register (B)+14h) will be

set to ‘1’, and an interrupt will be generated to the host.

When this happens, the interrupt must be serviced be-

fore another command may be written to the Command

Register.

An Invalid command is defined as a command written to

the Am79C974 that is either not supported, not allowed

in the specified mode, or a command that has an unsup-

ported command mode.

The following conditions will also cause an Invalid Com-

mand interrupt to occur:

An Initiator Information Transfer, Transfer Pad, or

Command Complete is issued when

ACK

is still

asserted.

A Selection command is issued with the DMA bit

enabled, if the Selection command was previously

issued with the DMA enabled.

Command Window

The window at the point where the Disable Selection/

Reselection command (45h/C5h) has been loaded into

the Command Register ((B)+0Ch), and before bus-initi-

ated Selection begins, has been eliminated. This pre-

vents a false Successful Operation Interrupt from being

generated when the Selection sequence continues to

completion after the Disable command has been

loaded.

Initiator Commands

Initiator commands are executed by the device when it

is in the Initiator mode. If the device is not in the Initiator

mode and an Initiator command is received the device

will ignore the command, generate an Invalid Command

interrupt and clear the Command Register.

Should the Target disconnect from the SCSI bus by

deasserting the

BSY

signal line while the Am79C974

(Initiator) is waiting for the Target to assert

REQ

, a Dis-

connected Interrupt will be issued 1.5 to 3.5 clock cycles

following

BSY

going false.

Upon receipt of the last byte during Message In phase,

ACK

will remain asserted to prevent the Target from is-

suing any additional bytes, while the Initiator decides to

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C975KCW | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C974KC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C974KC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C974KCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。