- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄171234 > DSPA56371 (飛思卡爾半導體(中國)有限公司) SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs PDF資料下載

參數(shù)資料

| 型號: | DSPA56371 |

| 廠商: | 飛思卡爾半導體(中國)有限公司 |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| 中文描述: | SigmaDSP的28-/56-Bit音頻處理器雙ADC和4個DAC |

| 文件頁數(shù): | 31/124頁 |

| 文件大?。?/td> | 1752K |

| 代理商: | DSPA56371 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁

14

DSP56371 Technical Data

Freescale Semiconductor

Signal/Connection Descriptions

3.7

Serial Host Interface

The SHI has five I/O signals that can be configured to allow the SHI to operate in either SPI or I2C mode.

RESET

Input

Reset—RESET is an active-low, Schmitt-trigger input. When asserted, the

chip is placed in the Reset state and the internal phase generator is reset. The

Schmitt-trigger input allows a slowly rising input (such as a capacitor charging)

to reset the chip reliably. When the RESET signal is deasserted, the initial chip

operating mode is latched from the MODA, MODB, MODC and MODD inputs.

The RESET signal must be asserted during power up. A stable EXTAL signal

must be supplied while RESET is being asserted.

Internal Pull up resistor.

This input is 5 V tolerant.

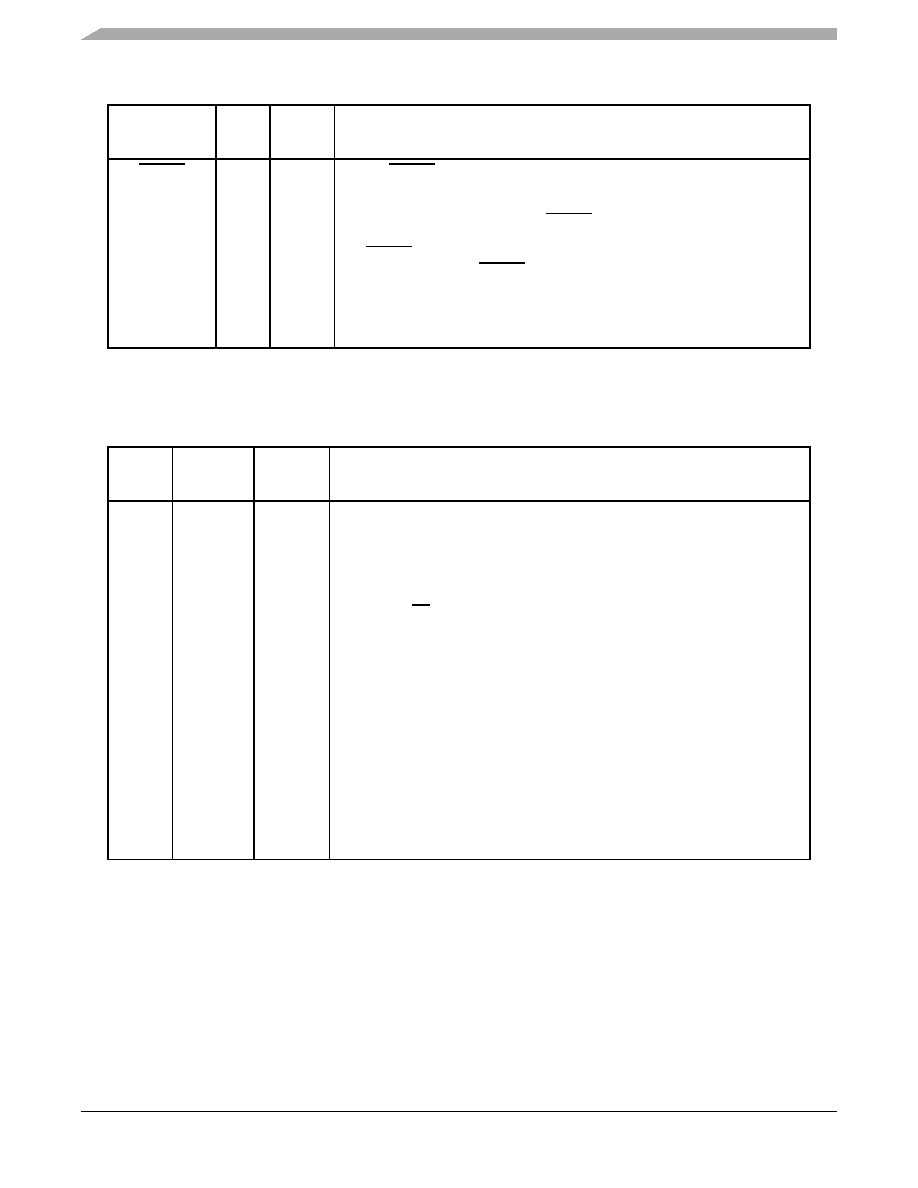

Table 7. Serial Host Interface Signals

Signal

Name

Signal

Type

State

during

Reset

Signal Description

SCK

Input or

output

Tri-stated

SPI Serial Clock—The SCK signal is an output when the SPI is configured as a

master and a Schmitt-trigger input when the SPI is configured as a slave. When

the SPI is configured as a master, the SCK signal is derived from the internal

SHI clock generator. When the SPI is configured as a slave, the SCK signal is

an input, and the clock signal from the external master synchronizes the data

transfer. The SCK signal is ignored by the SPI if it is defined as a slave and the

slave select (SS) signal is not asserted. In both the master and slave SPI

devices, data is shifted on one edge of the SCK signal and is sampled on the

opposite edge where data is stable. Edge polarity is determined by the SPI

transfer protocol.

SCL

Input or

output

I2C Serial Clock—SCL carries the clock for I2C bus transactions in the I2C

mode. SCL is a Schmitt-trigger input when configured as a slave and an open-

drain output when configured as a master. SCL should be connected to VDD

through a pull-up resistor.

This signal is tri-stated during hardware, software and individual reset. Thus,

there is no need for an external pull-up in this state.

Internal Pull up resistor.

This input is 5 V tolerant.

Table 6. Interrupt and Mode Control (Continued)

Signal Name

Type

State

During

Reset

Signal Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSR-09 | PIANO DIP SWITCH-9SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-STRAIGHT |

| DA-12 | PIANO DIP SWITCH-12SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-RIGHT ANGLE |

| DP-10T | PIANO DIP SWITCH-10SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-RIGHT ANGLE |

| DS-03T | PIANO DIP SWITCH-3SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-STRAIGHT |

| DS-06 | PIANO DIP SWITCH-6SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-STRAIGHT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSPA56371AF150 | 制造商:Freescale Semiconductor 功能描述:DSP FIXED-POINT 24-BIT 150MHZ 150MIPS 80-PIN LQFP TRAY - Trays |

| DSPA56371AF180 | 制造商:Freescale Semiconductor 功能描述:DSP FIXED-POINT 24-BIT 181MHZ 181MIPS 80-PIN LQFP TRAY - Trays |

| DSPA56720AG | 制造商:Freescale Semiconductor 功能描述:DSP FIXED-POINT 24-BIT 200MHZ 200MIPS 144-PIN LQFP TRAY - Trays |

| DSPA56721AF | 制造商:Freescale Semiconductor 功能描述:DSP FIXED-POINT 24-BIT 200MHZ 200MIPS 80-PIN LQFP TRAY - Bulk |

| DSPA56721AG | 制造商:Freescale Semiconductor 功能描述:AUD PROCESSOR 144LQFP - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。