- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄171234 > DSPA56371 (飛思卡爾半導(dǎo)體(中國)有限公司) SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs PDF資料下載

參數(shù)資料

| 型號(hào): | DSPA56371 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| 中文描述: | SigmaDSP的28-/56-Bit音頻處理器雙ADC和4個(gè)DAC |

| 文件頁數(shù): | 66/124頁 |

| 文件大?。?/td> | 1752K |

| 代理商: | DSPA56371 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁當(dāng)前第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁

46

DSP56371 Technical Data

Freescale Semiconductor

Enhanced Serial Audio Interface Timing

14

Enhanced Serial Audio Interface Timing

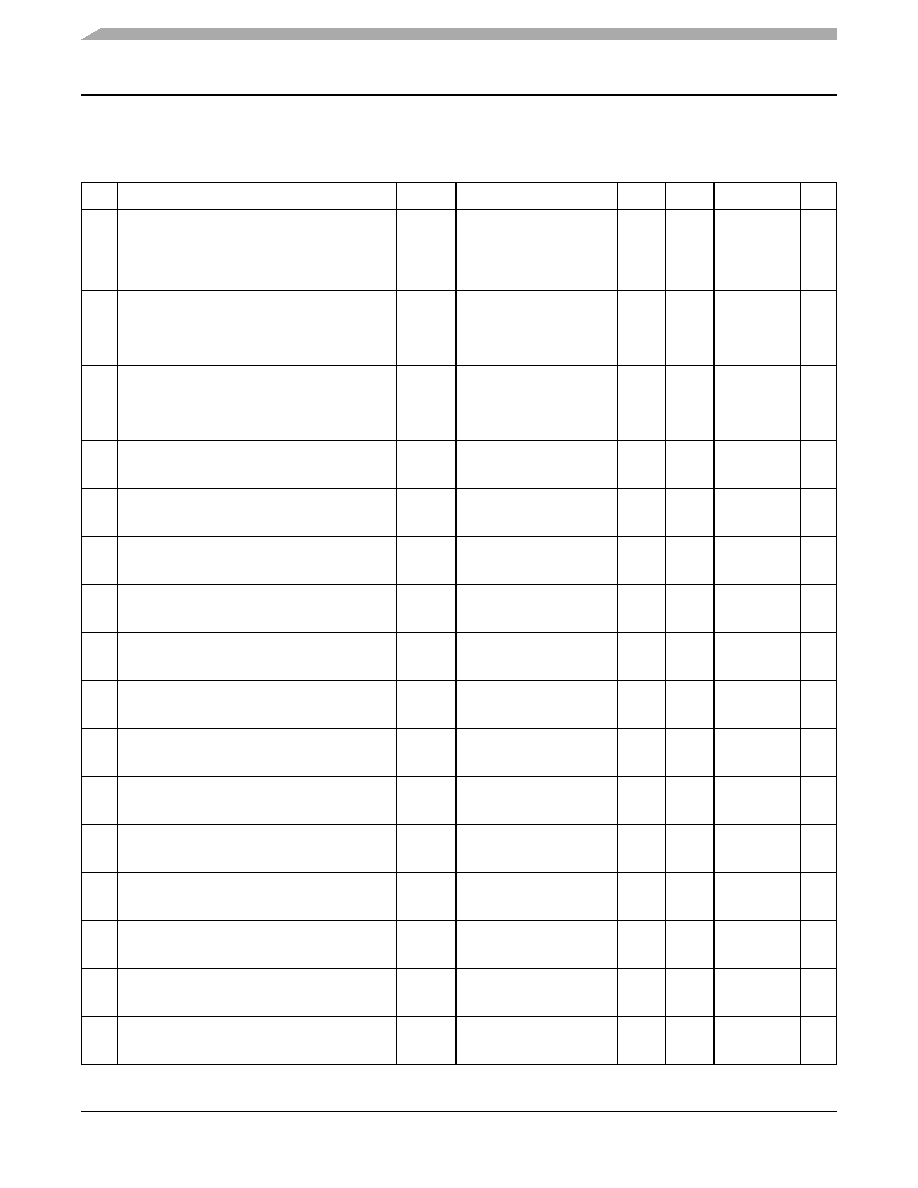

Table 22. Enhanced Serial Audio Interface Timing

No.

Characteristics1, 2, 3

Symbol

Expression3

Min

Max

Condition4

Unit

62

Clock cycle5

tSSICC

4

× Tc

22.3

—

i ck

ns

4

× Tc

22.3

—

x ck

SCKT:max[(3*TC) or t87]

26.5

—

x ck

63

Clock high period

For internal clock

—

2

× Tc 10.0

3.4

—

ns

For external clock

2

× Tc

10.0

—

64

Clock low period

For internal clock

—

2

× Tc 10.0

3.4

—

ns

For external clock

2

× Tc

10.0

—

65

SCKR rising edge to FSR out (bl) high

—

37.0

22.0

x ck

i ck a

ns

66

SCKR rising edge to FSR out (bl) low

—

37.0

22.0

x ck

i ck a

ns

67

SCKR rising edge to FSR out (wr) high6

——

—

39.0

24.0

x ck

i ck a

ns

68

SCKR rising edge to FSR out (wr) low6

——

—

39.0

24.0

x ck

i ck a

ns

69

SCKR rising edge to FSR out (wl) high

—

36.0

21.0

x ck

i ck a

ns

70

SCKR rising edge to FSR out (wl) low

—

37.0

22.0

x ck

i ck a

ns

71

Data in setup time before SCKR (SCK in

synchronous mode) falling edge

——

0.0

19.0

—

x ck

i ck

ns

72

Data in hold time after SCKR falling edge

—

5.0

3.0

—

x ck

i ck

ns

73

FSR input (bl, wr) high before SCKR falling

edge 6

——

1.0

23.0

—

x ck

i ck a

ns

74

FSR input (wl) high before SCKR falling edge

—

1.0

23.0

—

x ck

i ck a

ns

75

FSR input hold time after SCKR falling edge

—

3.0

0.0

—

x ck

i ck a

ns

76

Flags input setup before SCKR falling edge

—

0.0

19.0

—

x ck

i ck s

ns

77

Flags input hold time after SCKR falling edge

—

6.0

0.0

—

x ck

i ck s

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSR-09 | PIANO DIP SWITCH-9SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-STRAIGHT |

| DA-12 | PIANO DIP SWITCH-12SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-RIGHT ANGLE |

| DP-10T | PIANO DIP SWITCH-10SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-RIGHT ANGLE |

| DS-03T | PIANO DIP SWITCH-3SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-STRAIGHT |

| DS-06 | PIANO DIP SWITCH-6SWITCHES, SPST, LATCHED,0.05A, 24VDC, THROUGH HOLE-STRAIGHT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSPA56371AF150 | 制造商:Freescale Semiconductor 功能描述:DSP FIXED-POINT 24-BIT 150MHZ 150MIPS 80-PIN LQFP TRAY - Trays |

| DSPA56371AF180 | 制造商:Freescale Semiconductor 功能描述:DSP FIXED-POINT 24-BIT 181MHZ 181MIPS 80-PIN LQFP TRAY - Trays |

| DSPA56720AG | 制造商:Freescale Semiconductor 功能描述:DSP FIXED-POINT 24-BIT 200MHZ 200MIPS 144-PIN LQFP TRAY - Trays |

| DSPA56721AF | 制造商:Freescale Semiconductor 功能描述:DSP FIXED-POINT 24-BIT 200MHZ 200MIPS 80-PIN LQFP TRAY - Bulk |

| DSPA56721AG | 制造商:Freescale Semiconductor 功能描述:AUD PROCESSOR 144LQFP - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。