- 您現(xiàn)在的位置:買賣IC網 > PDF目錄370702 > HSP3824VI (Harris Corporation) Direct Sequence Spread Spectrum Baseband Processor PDF資料下載

參數資料

| 型號: | HSP3824VI |

| 廠商: | Harris Corporation |

| 元件分類: | 基帶處理器 |

| 英文描述: | Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | 直接序列擴頻基帶處理器 |

| 文件頁數: | 29/41頁 |

| 文件大?。?/td> | 276K |

| 代理商: | HSP3824VI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

29

HSP3824

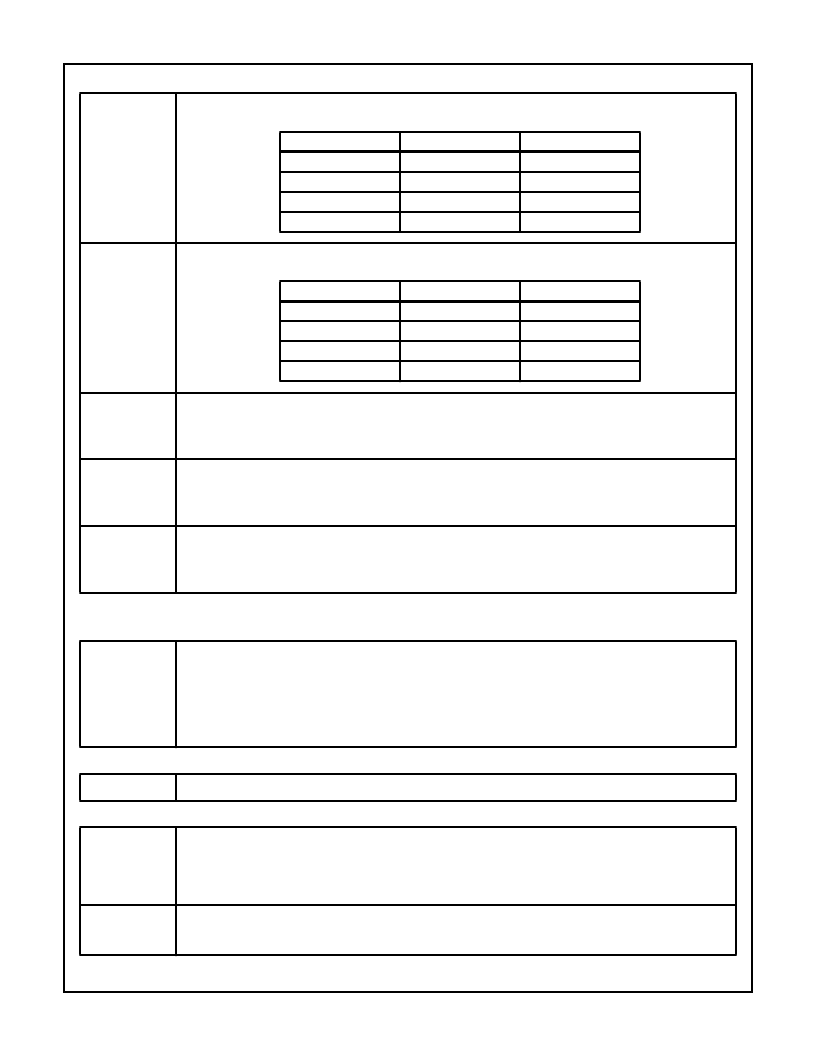

Bit 6, 5

These control bits combined are used to select the number of chips per symbol used in the I and Q transmit paths (see

table below).

Bit 4, 3

These control bits are used to select the divide ratio for the transmit chip clock timing.

NOTE:

The value of N is determined by the following equation: Symbol Rate = MCLK/(N x Chips per symbol)

Bit 2

This control bit is used to select the origination of Preamble/Header information.

Logic 1: The HSP3824 generates the Preamble and Header internally by formatting the programmed header

information and generating a TX_RDY to indicate the beginning of the data packet.

Logic 0: Accepts the Preamble/Header information from an externally generated source.

Bit 1

This control bit is used to indicate the signal modulation type for the transmitted data packet. When configured for mode

0 header, or mode 3 and external header, this bit is ignored. See Register 0 bits 4 and 3.

Logic 1 = DBPSK modulation for data packet.

Logic 0 = DQPSK modulation for data packet.

Bit 0

This control bit is used to indicate the signal modulation type for the received data packet Used only with header modes

1 and 2. See register 2 bits 1 and 0.

Logic 1 = DBPSK.

Logic 0 = DQPSK.

CONFIGURATION REGISTER 4 ADDRESS (10h) INTERNAL TEST REGISTER A

Bit 7 - 0

These control bits are used to direct various internal signals to test port output pins. These internal signals are moni-

tored to fault isolate the device at manufacturing testing. During normal operation, the value 0h is recommended. This

will result to the following signals becoming available at the output test pins of the device:

Pin 46 (TEST7): Carrier Sense (CRS), a Logic 1 indicates PN lock.

Pin 45 (TEST6): Energy Detect (ED), a Logic 1 indicates that there is energy detected in the channel. The ED goes

active when the RSSI exceeds the threshold level programmed by the user.

Pin 1 (TEST_CK): PN clock.

CONFIGURATION REGISTER 5 ADDRESS (14h,18h) INTERNAL TEST REGISTER B

Bits 7 - 0

These bits need to be programmed to 0h. They are used for manufacturing test only.

CONFIGURATION REGISTER 7 ADDRESS (1Ch) MODEM STATUS REGISTER A

Bit 7

This bit indicates the status of the TX_RDY output pin. TX_RDY is used only when the HSP3824 generates the Pre-

amble/Header data internally.

Logic 1: Indicates that the HSP3824 has completed transmitting Preamble header information and is ready to accept

data from the external source (i.e. MAC) to transmit.

Logic 0: Indicates that the HSP3824 is in the process of transmitting Preamble Header information.

Bit 6

This status bit indicates the antenna selected by the device.

Logic 0: Antenna A is selected.

Logic 1: Antenna B is selected.

CONFIGURATION REGISTER 3 ADDRESS (0Ch) MODEM CONFIGURATION REGISTER D (Continued)

CHIPS PER

BIT 6

BIT 5

11

0

0

13

0

1

15

1

0

16

1

1

MASTER

BIT 4

BIT 3

N = 2

0

0

N = 4

0

1

N = 8

1

0

N = 16

1

1

相關PDF資料 |

PDF描述 |

|---|---|

| HSR101 | Silicon Schottky Barrier Diode for Various detector, High speed switching(用于多種檢波和高速開關的肖特基勢壘二極管) |

| HSRD1056RH165S | Converter IC |

| HSRD1056RH169H | Converter IC |

| HSRD1056RH169S | Converter IC |

| HSRD1056RH240H | Converter IC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HSP3824VI96S5001 | 制造商:Harris Corporation 功能描述: |

| HSP40223221 | 制造商:PARMAR 功能描述:BALLAST HPS/MH 400W 制造商:PARMAR 功能描述:BALLAST, HPS/MH, 400W |

| HSP4070C | 制造商:JLWORLD 制造商全稱:JLWORLD 功能描述:SPEAKER SOUND GENERATORS |

| HSP40G-8 | 制造商:JLWORLD 制造商全稱:JLWORLD 功能描述:SPEAKER SOUND GENERATORS |

| HSP43124 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Serial I/O Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復。